(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАТРИЦЫ НЕПОЛНОГО ПАРАЛЛЕЛИЗМА | 2009 |

|

RU2421804C2 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1336123A1 |

| Устройство для контроля блоков оперативной памяти | 1990 |

|

SU1751821A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| МИКРОЭВМ | 1991 |

|

SU1819017A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1809398A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

Изобретение относится к вычислительной технике и может быть использовано в составе устройств контроля памяти в серийном производстве и при испытаниях. Целью изобретения является расширение области применения устройства за счет обеспечения контроля блоков памяти динамического типа. Устройство содержит первый, второй и третий счетные триггеры, элементы И-НЕ с первого по четвертый, элемент И, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ с первого по пятый, первый, второй и третий элементы ИЛИ, первый и второй элементы ИЛИ-НЕ, элемент задержки и мультиплексор. Цель изобретения достигается тем, что в зависимости от режима работы устройство формирует на своих выходах сигналы, соответствующие временным диаграммам памяти статического либо динамического типа.2 мл

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля памяти в серийном производстве и при испытаниях.

Целью изобретения является расширение области применения устройства за счет обеспечения контроля блоков памяти динамического типа.

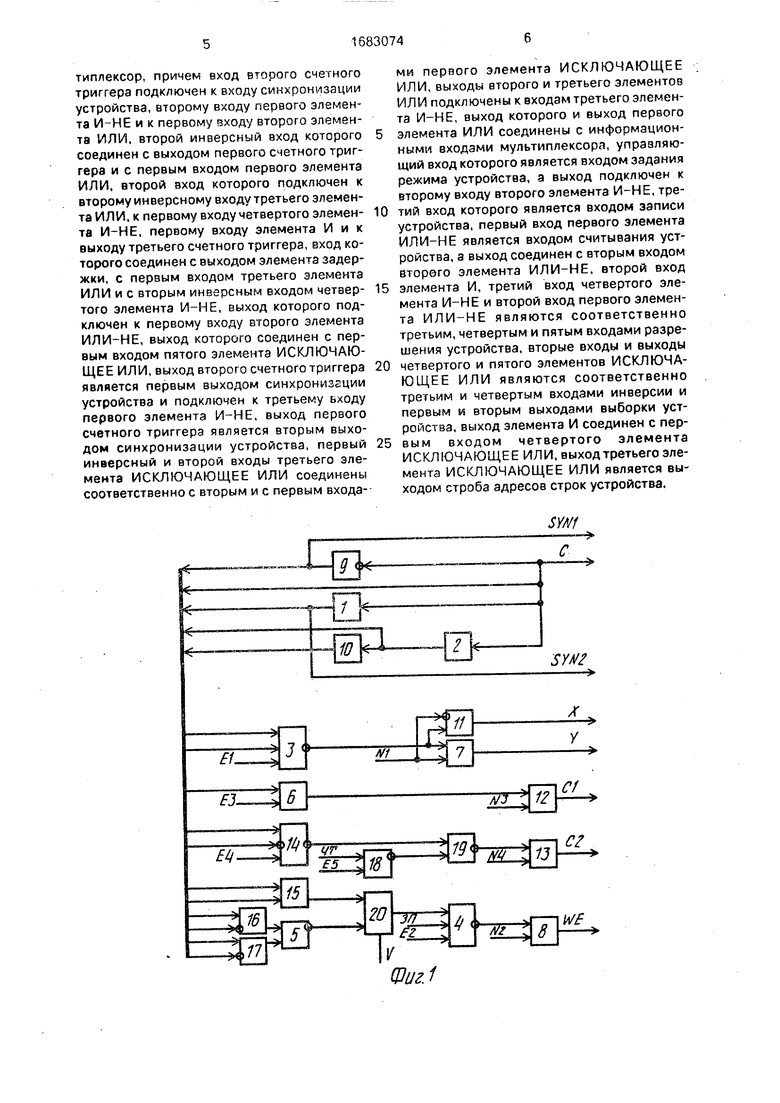

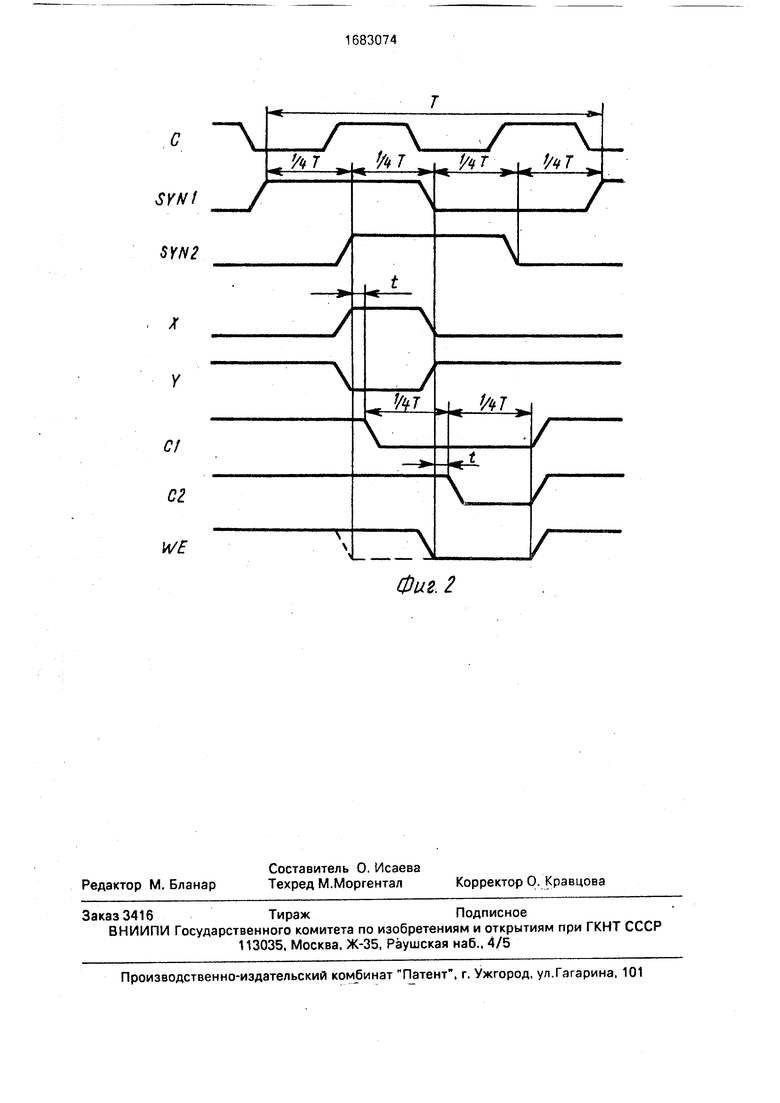

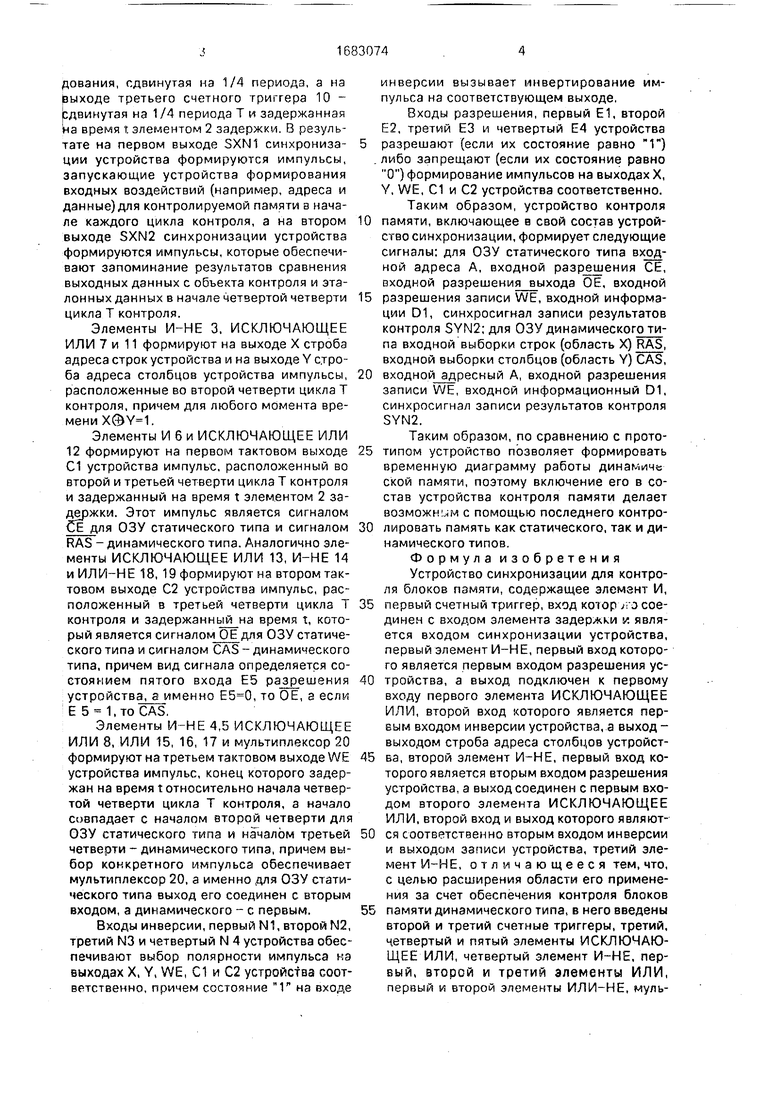

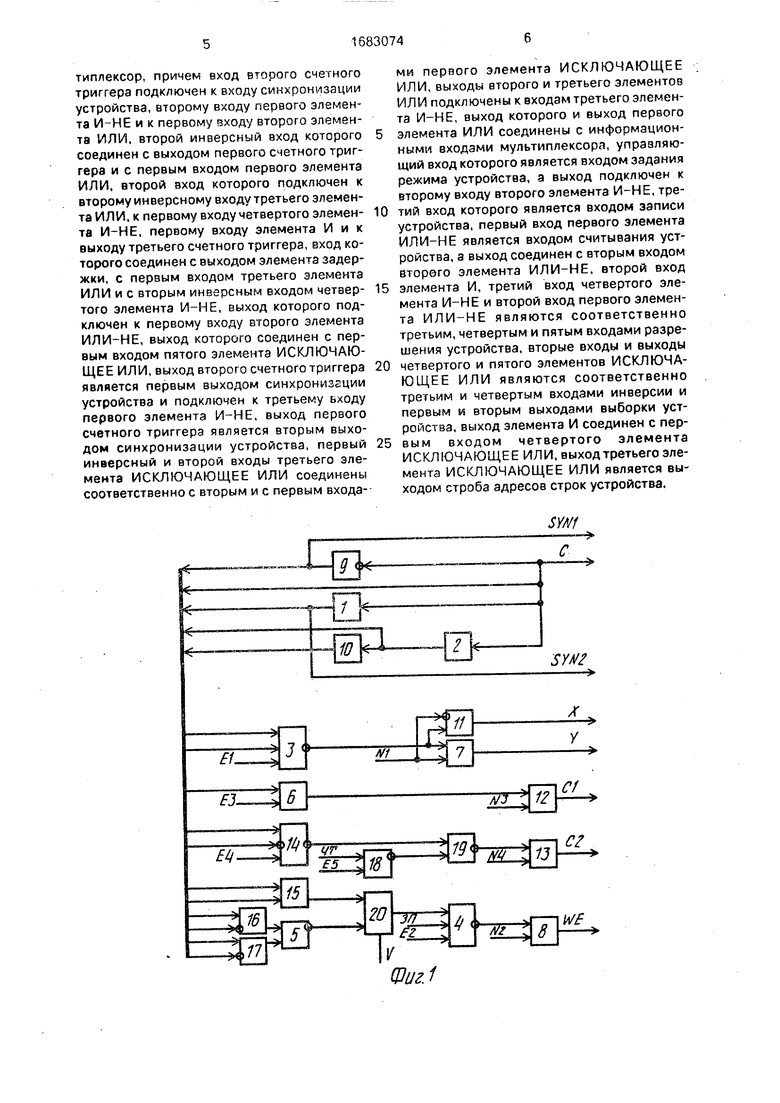

На фиг. 1 изображена схема устройства синхронизации для контроля блоков памяти; на фиг, 2 - временная диаграмма его работы.

Устройство (фиг. 1) содержит первый счетный триггер 1, элемент 2 задержки, первый 3, второй 4, третий 5 элементы И-НЕ. элемент И 6, первый 7 и второй 8 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ,- второй 9. и третий 10 счетные триггеры, третий 11, четвертый 12 и пятый 13 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ. четвертый элемент И-НЕ 14, первый 15, второй 16 и третий 17 элементы ИЛИ, первый 18 и второй 19 элементы ИЛИ-НЕ, мультиплексор 20.

Устройство работает следующим образом.

На вход С синхронизации устройства поступают импульсы синхронизации с периодом следования, в два раза меньшим периода Т контроля (фиг. 2). Эти импульсы поступают на первый 1 и второй 9 триггеры и через элемент 2 задержки на триггер 10, причем первый 1 и третий 10 счетные триггеры срабатывают по фронту, а второй 9 счетный триггер - по срезу импульса синхронизации. Таким образом, на выходе второго счетного триггера 9 формируется последовательность импульсов с периодом следования, равным периоду Т контроля, на выходе первого счетного триггера 1 - последовательность импульсов с периодом Т елеО 00

CJ

о

2

дования, сдвинутая на 1/4 периода, а на рыходе третьего счетного триггера 10 - (сдвинутая на 1/4 периода Т и задержанная на время т элементом 2 задержки. В результате на первом выходе SXN1 синхрониза- ции устройства формируются импульсы, запускающие устройства формирования входных воздействий (например, адреса и данные) для контролируемой памяти в начале каждого цикла контроля, а на втором выходе SXN2 синхронизации устройства формируются импульсы, которые обеспечивают запоминание результатов сравнения выходных данных с объекта контроля и эталонных данных в начале четвертой четверти цикла Т контроля.

Элементы И-НЕ 3. ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 11 формируют на выходе X строба адреса строк устройства и на выходе Y строба адреса столбцов устройства импульсы, расположенные во второй четверти цикла Т контроля, причем для любого момента времени .

Элементы И 6 и ИСКЛЮЧАЮЩЕЕ ИЛИ 12 формируют на первом тактовом выходе С1 устройства импульс, расположенный во второй и третьей четверти цикла Т контроля и задержанный на время t элементом 2 задержки. Этот импульс является сигналом СЕ для ОЗУ статического типа и сигналом RAS -динамического типа. Аналогично элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 13, И-НЕ 14 и ИЛИ-НЕ 18, 19 формируют на втором тактовом выходе С2 устройства импульс, расположенный в третьей четверти цикла Т контроля и задержанный а время t, который является сигналом ОЕ для ОЗУ статического типа и сигналом CAS - динамического типа, причем вид сигнала определяется состоянием пятого входа Е5 ра зр ешения устройства, а именно , то ОЕ, а если Е 5 1, то CAS.

Элементы И-НЕ 4,5 ИСКЛЮЧАЮЩЕЕ ИЛИ 8, ИЛИ 15, 16, 17 и мультиплексор 20 формируют на третьем тактовом выходе WE устройства импульс, конец которого задержан на время t относительно начала четвертой четверти цикла Т контроля, а начало совпадает с началом второй четверти для ОЗУ статического типа и началом третьей четверти - динамического типа, причем выбор конкретного импульса обеспечивает мультиплексор 20, а именно для ОЗУ статического типа выход его соединен с вторым входом, а динамического - с первым.

Входы инверсии, первый N1, второй N2, третий N3 и четвертый N 4 устройства обеспечивают выбор полярности импульса на выходах X, Y, WE, С1 и С2 устройства соответственно, причем состояние 1 на входе

инверсии вызывает инвертирование импульса на соответствующем выходе,

Входы разрешения, первый Е1, второй Е2, третий ЕЗ и четвертый Е4 устройства разрешают (если их состояние равно 1) либо запрещают (если их состояние равно О) формирование импульсов на выходах X, Y, WE, С1 и С2 устройства соответственно. Таким образом, устройство контроля памяти, включающее в свой состав устройство синхронизации, формирует следующие сигналы: для ОЗУ статического типа входной адреса А, входной разрешения СЕ, входной разрешения выхода ОЕ, входной разрешения записи WE, входной информации D1, синхросигнал записи результатов контроля SYN2; для ОЗУ динамического ти- па входной выборки строк (область X) RAS, входной выборки столбцов (область Y) CAS, входной адресный А, входной разрешения записи WE, входной информационный D1, синхросигнал записи результатов контроля SYN2.

Таким образом, по сравнению с прототипом устройство позволяет формировать временную диаграмму работы динамиче ской памяти, поэтому включение его в состав устройства контроля памяти делает возможном с помощью последнего контролировать память как статического, так и динамического типов.

Формула изобретения Устройство синхронизации для контроля блоков памяти, содержащее элемант И, первый счетный триггер, вход котор о соединен с входом элемента задержки у. является входом синхронизации устройства, первый элемент И-НЕ, первый вход которого является первым входом разрешения устройства, а выход подключен к первому входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является первым входом инверсии устройства, а выход - выходом строба адреса столбцов устройства, второй элемент И-НЕ, первый вход которого является вторым входом разрешения устройства, а выход соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход и выход которого являются соотвртственно вторым входом инверсии и выходом записи устройства, третий элемент И-НЕ, отличающееся тем, что, с целью расширения области его применения за счет обеспечения контроля блоков памяти динамического типа, в него введены второй и третий счетные триггеры, третий, четвертый и пятый элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, четвертый элемент И-НЕ, первый, второй и третий элементы ИЛИ, первый и второй элементы ИЛИ-НЕ, мультиплексор, причем вход второго счетного триггера подключен к входу синхронизации устройства, второму входу первого элемента И-НЕ и к первому входу второго элемента ИЛИ, второй инверсный вход которого соединен с выходом первого счетного триггера и с первым входом первого элемента ИЛИ, второй вход которого подключен к второму инверсному входу третьего элемента ИЛИ, к первому входу четвертого элемента И-НЕ, первому входу элемента И и к выходу третьего счетного триггера, вход которого соединен с выходом элемента задержки, с первым входом третьего элемента ИЛИ и с вторым инверсным входом четвертого элемента И-НЕ, выход которого подключен к первому входу второго элемента ИЛИ-НЕ, выход которого соединен с первым входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго счетного триггера является первым выходом синхронизации устройства и подключен к третьему ьходу первого элемента И-НЕ, выход первого счетного триггера является вторым выходом синхронизации устройства, первый инверсный и второй входы третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственное вторым и с первым входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы второго и третьего элементов ИЛИ подключены к входам третьего элемента И-НЕ, выход которого и выход первого

элемента ИЛИ соединены с информационными входами мультиплексора, управляющий вход которого является входом задания режима устройства, а выход подключен к второму входу второго элемента И-НЕ, третий вход которого является входом записи устройства, первый вход первого элемента ИЛИ-НЕ является входом считывания устройства, а выход соединен с вторым входом второго элемента ИЛИ-НЕ, второй вход

элемента И, третий вход четвертого элемента И-НЕ и второй вход первого элемента ИЛИ-НЕ являются соответственно третьим, четвертым и пятым входами разрешения устройства, вторые входы и выходы

четвертого и пятого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответственно третьим и четвертым входами инверсии и первым и вторым выходами выборки устройства, выход элемента И соединен с первым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является выходом строба адресов строк устройства.

Фиг.1

Фиг. 2

| Многоканальное устройство для контроля памяти | 1984 |

|

SU1238164A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля памяти | 1987 |

|

SU1587598A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-10-07—Публикация

1989-03-30—Подача