20

VI

О

ел

00

vi

с

Изобретение относится к области вычислительной техники и может быть использовано для функционального контроля блоков оперативной памяти.

Целью изобретения является повышение достоверности контроля устройства.

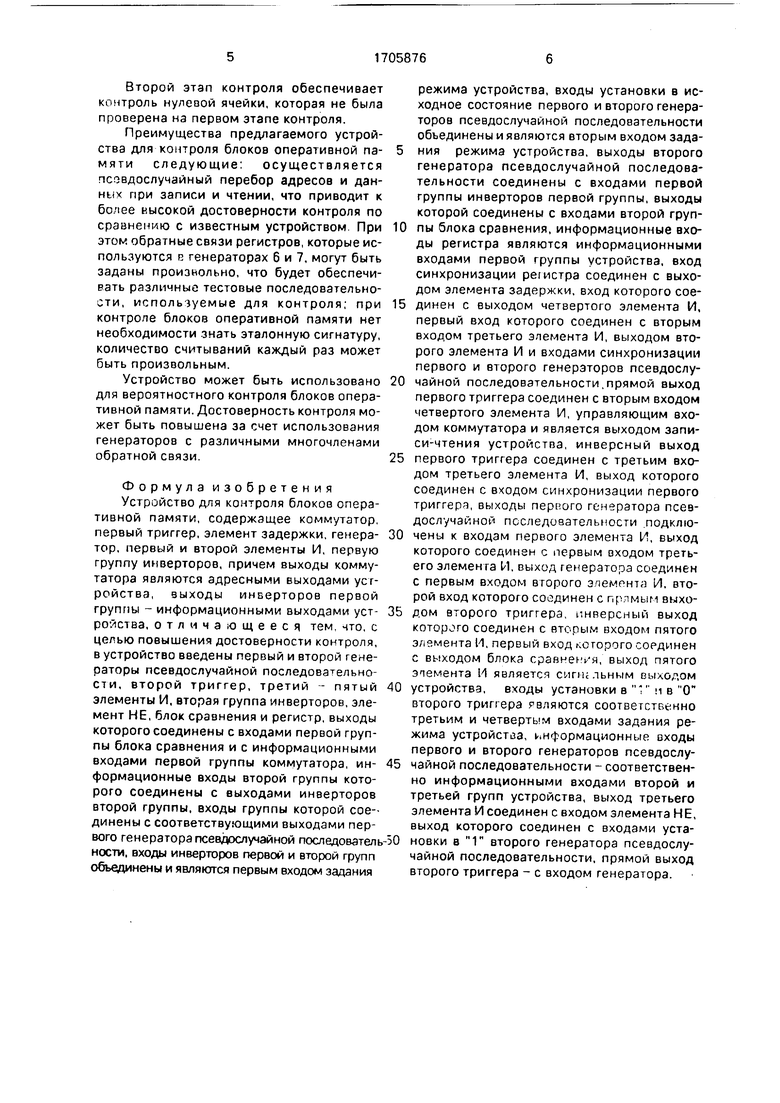

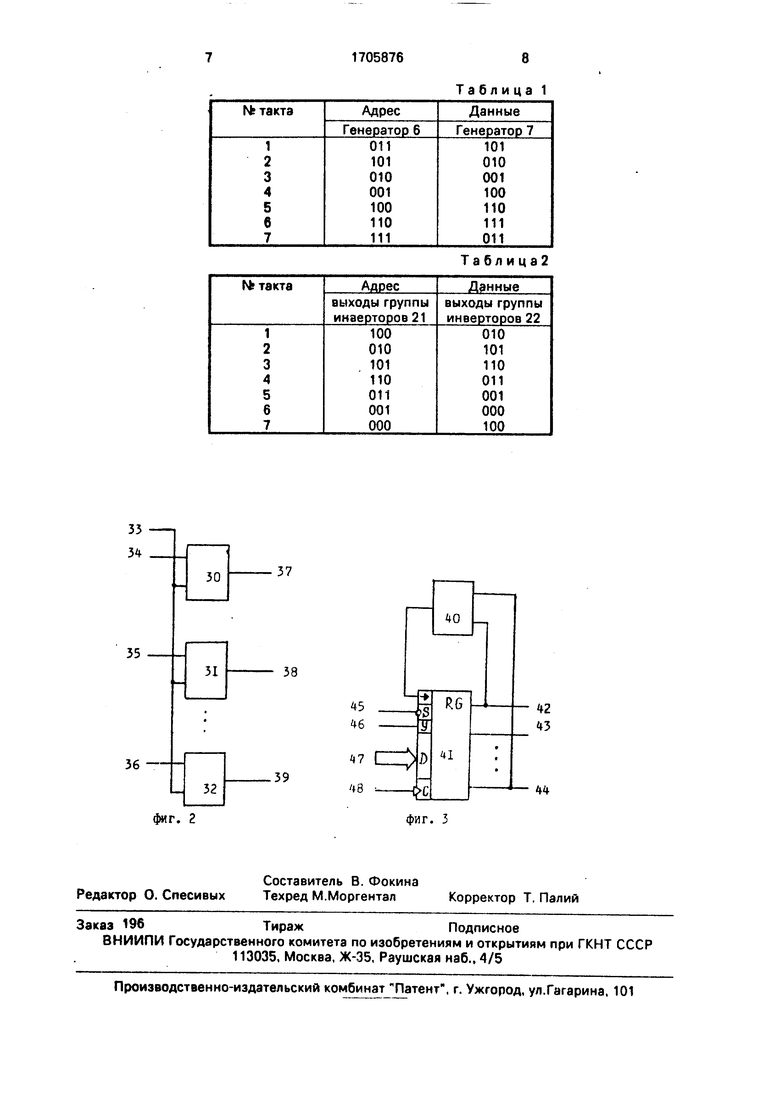

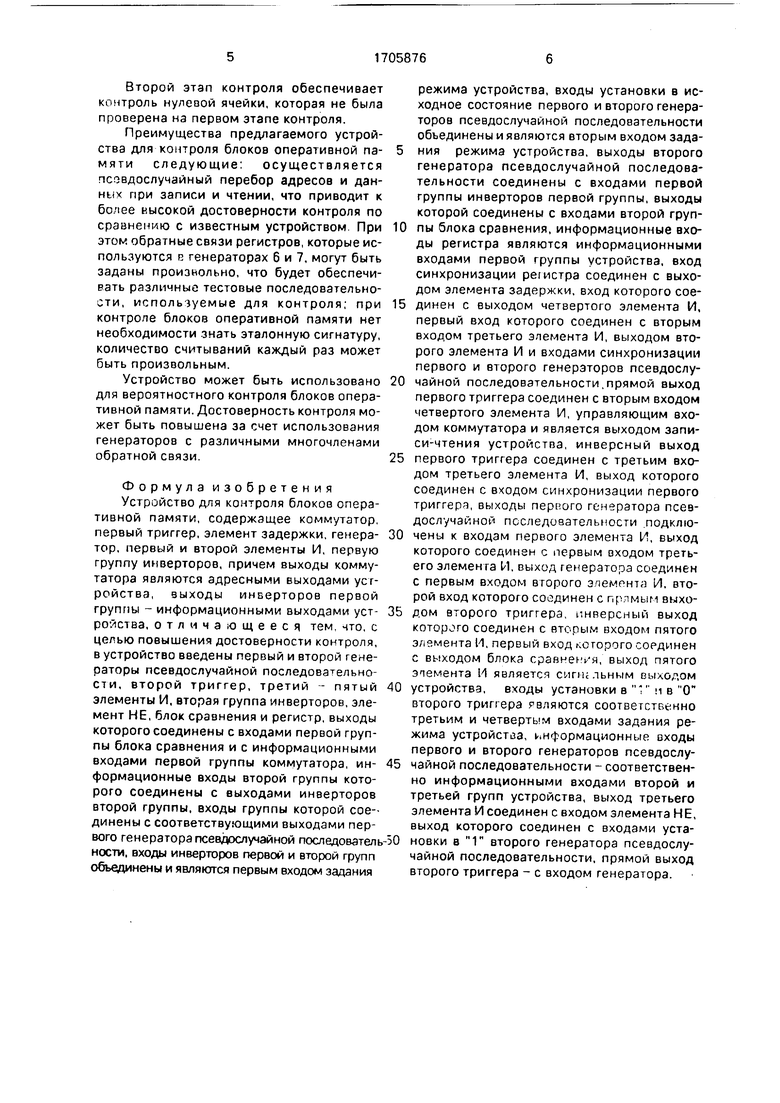

На фиг, 1 приведена функциональная схема устройства для контроля блоков оперативной памяти; на фиг. 2 - функциональная схема группы инверторов; на фиг. 3 - функциональная схема генератора псевдослучайной последовательности,

На фиг, 1-3 обозначены: элементы И1-5, первый 6 и второй 7 генераторы псевдослучайной последовательности, коммутатор 8, проверяемый 9 блок оперативной памяти, регистр 10, генератор 11, триггеры 12 и 13, элемент 14 задержки, блок 15 сравнения, первый 16, второй 17, третий 18 и четвертый 19 входы задания режима устройства, сигнальный выход 20 устройства, вторая 21 и первая 22 группа инверторов, информационные входы 23, 24, элемент НЕ 25, адресные 26 выходы устройства, выход записи-чтения 27 устройства, информационные выходы 28 устройства, информационные 29 входы устройства, сумматоры по модулю два 30-32, входы 33-36 группы интерторов, выходы 37-39 группы инверторов, сумматор по модулю два 40, регистр 41, выходы 42-44 генератора псевдослучайной последовательности, входы 45-48 генератора псевдослучайной последовательности.

Устройство работает следующим образом.

Необходимо отметить, что многочлены обратной связи генераторов 6 и 7 являются многочленами n-й степени, принадлежащие максимальному показателю. Это означает, что все ненулевые выходные последовательности имеют период 2п-1 (п - разрядность регистра, который используется в генераторе). Такой генератор называется генератором максимального периода.

Перед началом работы в генератор б записывается значение кода NI (асе единицы +1 , с учетом многочлен обратной связи), в генератор 7 значение кода N2 - NI +1. На вход 16 подается О, что означает, что контроль блока 9 памяти будет проводиться с прямыми значениями адресов и данных. Регистр 10 установлен в состояние 1 на его выходах, а триггер 13-е состояние О на его прямом выходе (цепи начальной установки регистра 10 и триггера 13 условно не показаны).

На фиг. 1 также условно не показан сигнал обращения к прозеряемому Блоку one ративной памяти, так как указанный сигнал

не влияет на достижение положительного эффекта.

При поступлении на вход 18 сигнала О, а на вход 19 сигнала 1 с генератора 11 на

входы синхронизации генератора 6 и 7 поступают синхроимпульсы. Тем самым начинается перебор всех состояний генераторов 6 и 7 с максимальным периодом. Триггер 13 установлен в О, что определяет режим за0 писи информации в проверяемый блок 9 памяти.

В табл. 1 приведен возможный пример изменения адресов и информации, которые поступают в блоке 9 для трех разрядного

5 генератора псевдослучайной последовательности.

Как видно из табл. 1, в адрес (011) записывается информация (101), т.е. адрес следующей ячейки блока 9 памяти и т.д. При

0 значении всех единиц на выходах генератора 6 сработает элемент И1, что приведет к тому, что синхроимпульсы с генератора 11 переключает триггер 13 в единичное состояние на прямом выходе. Тот же импульс

5 установит генератор 7 в единичное состояние на его выходах. Начинается режим считывания из блока 9 памяти.

В режиме считывания по адресу, определяемому регистром 10, считывается ин0 формация, которая записывается в тот же регистр 10. Так как первоначально регистр 10 был установлен в состояние 1 на его выходах, то считается информация (011) (см. табл. 1). Далее по адресу (011) считывается

5 (101, и т.д. Таким образом, осуществляется режим кольцевой проверки блока 9 оперативной памяти.

При поступлении на вход 19 О, а на вход 18 1 на прямом выходе триггера 12

0 установится О, что означает окончание проверки ОЗУ. На инверсном выходе триггера 12 установится 1. которая разрешает сравнение содержимого регистра 10 и генератора 7, который работает синхронно с ре5 гистром 10. Если содержимое регистра 10 и генератора 7 равно, то блок 9 памяти работает правильно, а противном случае - блок памяти неисправен.

Второй згап контроля заключается в

0 проверке блока 9 памяти с инверсными значениями адресов и данных. Для этого на вход 16 подается 1. Установка триггеров, регистра и генераторов 6 и 7 осуществляется так же, как и в предыдущем случае, за

5 исключением того, что регистр 10 устанавливается в состояние О на всех своих выходах.

В табл. 2 приведен возможный пример изменения адресов и информации, поступающей а блок 9 памяти при контроле.

Второй этап контроля обеспечивает контроль нулевой ячейки, которая не была проверена на первом этапе контроля.

Преимущества предлагаемого устройства для контроля блоков оперативной па- мяти следующие: осуществляется псевдослучайный перебор адресов и данных при записи и чтении, что приводит к более высокой достоверности контроля по сравнению с известным устройством. При этом обратные связи регистров, которые используются в генераторах 6 и 7, могут быть заданы произвольно, что будет обеспечивать различные тестовые последовательности, используемые для контроля; при контроле блоков оперативной памяти нет необходимости знать эталонную сигнатуру, количество считываний каждый раз может быть произвольным.

Устройство может быть использовано для вероятностного контроля блоков оперативной памяти. Достоверность контроля может быть повышена за счет использования генераторов с различными многочленами обратной связи.

Формула изобретения Устройство для контроля блоков оперативной памяти, содержащее коммутатор, первый триггер, элемент задержки, генера- тор, первый и второй элементы И, первую группу инверторов, причем выходы коммутатора являются адресными выходами устройства, выходы инверторов первой группы - информационными выходами уст- ройства, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены первый и второй генераторы псевдослучайной последовательности, второй триггер, третий - пятый элементы И, вторая группа инверторов, элемент НЕ, блок сравнения и регистр, выходы которого соединены с входами первой группы блока сравнения и с информационными входами первой группы коммутатора, ин- формационные входы второй группы которого соединены с выходами инверторов второй группы, входы группы которой соединены с соответствующими выходами первого генератора псевдослучайной последовател ности, входы инверторов первой и второй групп объединены и являются первым входом задания

режима устройства, входы установки в исходное состояние первого и второго генераторов псевдослучайной последовательности объединены и являются вторым входом задания режима устройства, выходы второго генератора псевдослучайной последовательности соединены с входами первой группы инверторов первой группы, выходы которой соединены с входами второй группы блока сравнения, информационные входы регистра являются информационными входами первой группы устройства, вход синхронизации регистра соединен с выходом элемента задержки, вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с вторым входом третьего элемента И, выходом второго элемента И и входами синхронизации первого и второго генераторов псевдослучайной последовательности,прямой выход первого триггера соединен с вторым входом четвертого элемента И, управляющим входом коммутатора и является выходом записи-чтения устройства, инверсный выход первого триггера соединен с третьим входом третьего элемента И, выход которого соединен с входом синхронизации первого триггера, выходы первого генератора псевдослучайной последовательности .подключены к входам первого элемента И, выход которого соединен с первым входом третьего элемента И, выход генератора соединен с первым входом второго элемента И, второй вход которого соединен с прямым выходом второго триггера, инверсный выход которого соединен с вторым входом пятого элемента И. первый вход которого соединен с выходом блока сравнения, выход пятого эпемента И является синильным выходом устройства, входы установки в и в О второго триггера являются соответственно третьим и четвертым входами задания режима устройства, информационные входы первого и второго генераторов псевдослучайной последовательности - соответственно информационными входами второй и третьей групп устройства, выход третьего элемента И соединен с входом элемента НЕ, выход которого соединен с входами установки в Г второго генератора псевдослучайной последовательности, прямой выход второго триггера - с входом генератора.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков оперативной многоразрядной памяти | 1990 |

|

SU1774380A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для динамического преобразования адресов | 1980 |

|

SU903878A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1283859A1 |

| Устройство для диагностического контроля оперативной памяти | 1991 |

|

SU1807525A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

Изобретение относится к вычислительной технике и может быть использовано для функционального контроля блоков оперативной памяти. Устройство содержит элементы И 1-5, первый 6 и второй 7 генераторы псевдослучайной последовательности, коммутатор 8, проверяемый блок 9 оперативной памяти, регистр 10, генератор 11, триггеры 12, 13, элемент задержки 14, блок 15 сравнения, первый 16, второй 17, третий 18 и четвертый 19 входы задания режима, сигнальный выход 20, вторую 21 и первую 22 группы инверторов, информационные входы 23, 24, элемент НЕ 25, адресные выходы 26 устройства, выход 27 записи чтения устройства, информационные выходы 28, информационные входы 29, Устройство позволяет формировать произвольные адресные и информационные последовательности, что позволяет повысить достоверность контроля блоков оперативной памяти. 2 табл., 3 ил. « Ё

31

38

36 -

Таблица2

RG

42

43

41

44

| Устройство для контроля оперативной памяти | 1983 |

|

SU1140179A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1336123A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-01-15—Публикация

1990-03-27—Подача