Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных системах обработки информации.

Целью изобретения является расширение области применения устройства за счет возможности сдвига информации, разрядность которой кратна N, N - разрядность устройства для сдвига информации.

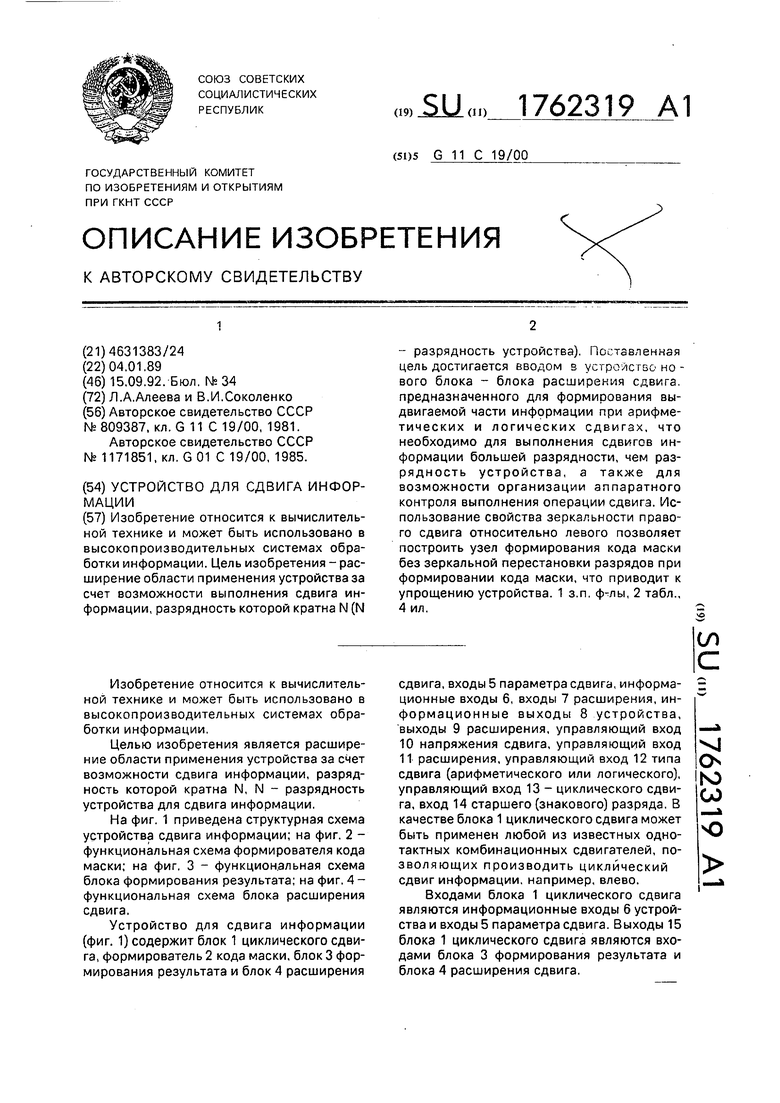

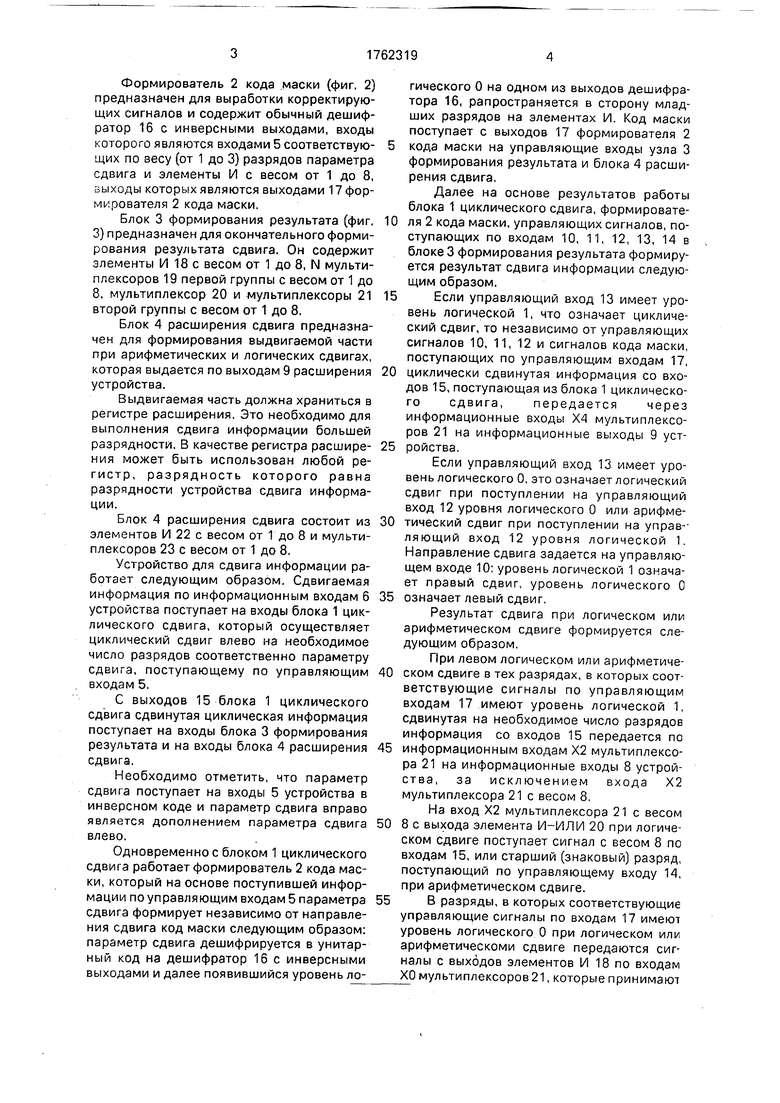

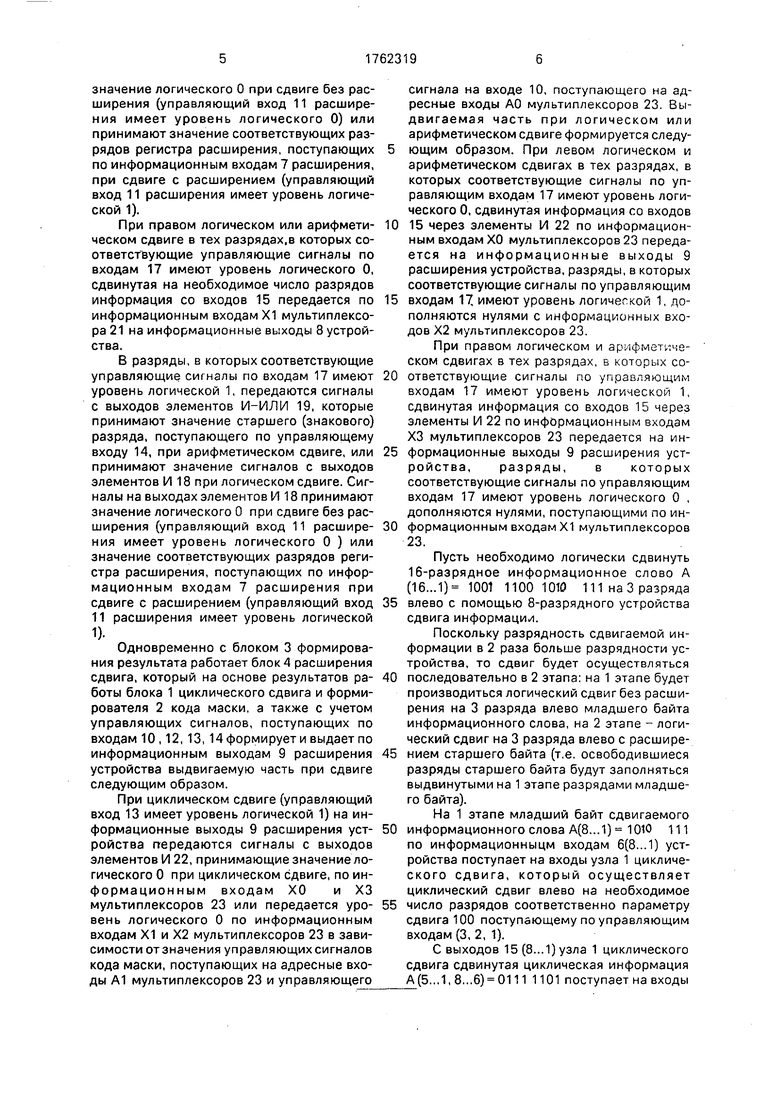

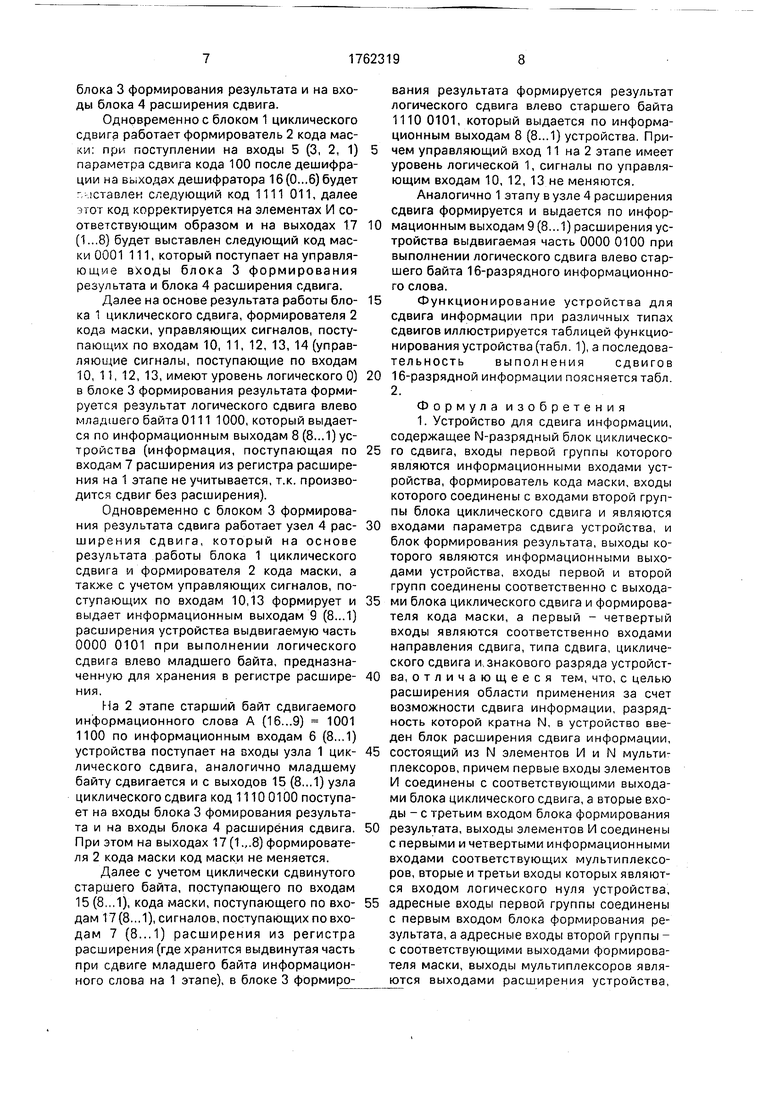

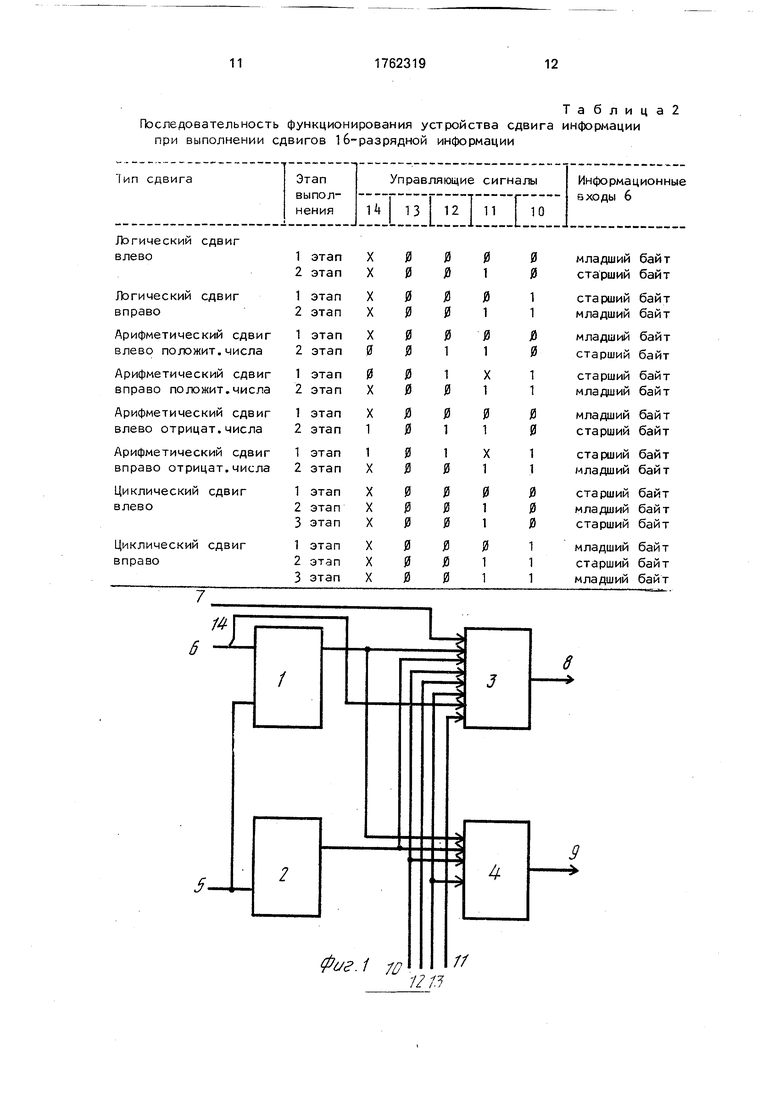

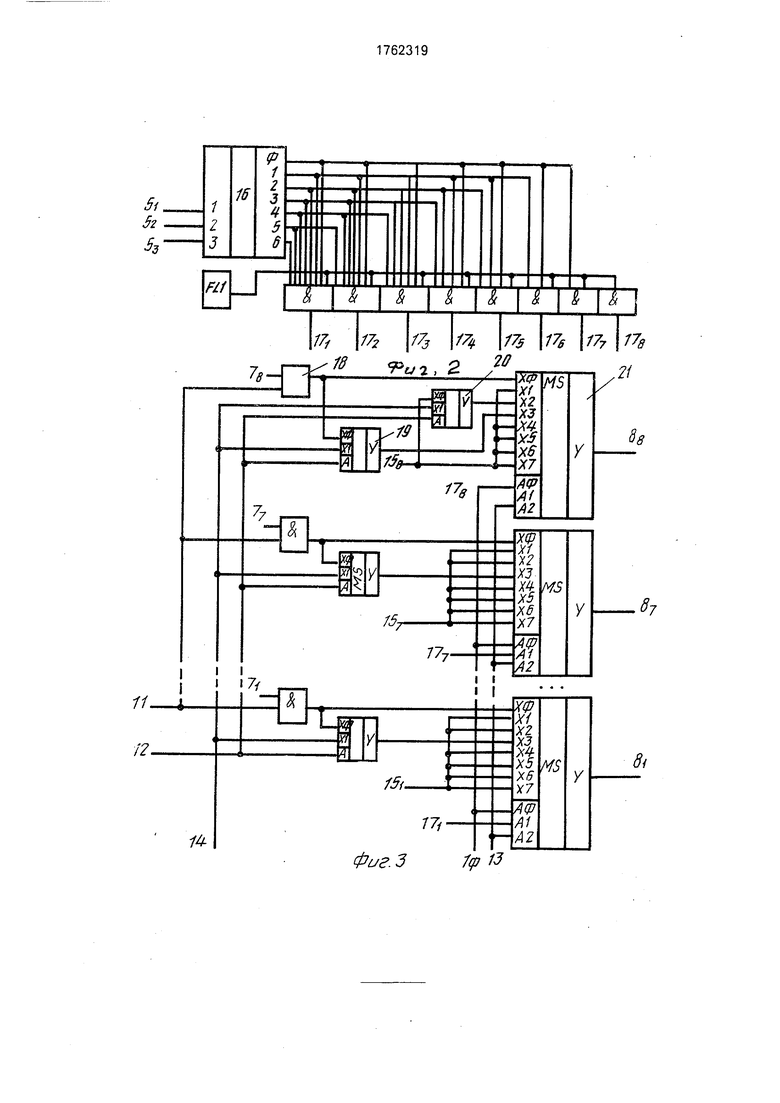

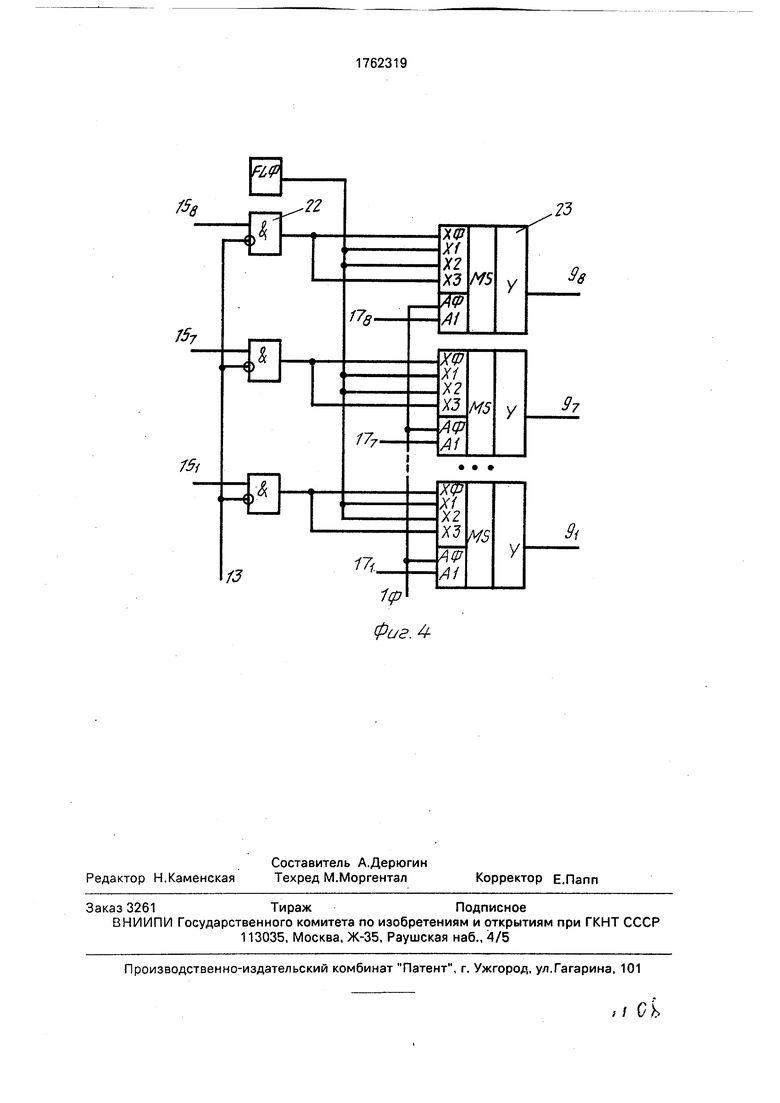

На фиг. 1 приведена структурная схема устройства сдвига информации; на фиг. 2 - функциональная схема формирователя кода маски; на фиг, 3 - функциональная схема блока формирования результата; на фиг, 4 - функциональная схема блока расширения сдвига.

Устройство для сдвига информации (фиг. 1) содержит блок 1 циклического сдвига, формирователь 2 кода маски, блок 3 формирования результата и блок 4 расширения

сдвига, входы 5 параметра сдвига, информационные входы 6, входы 7 расширения, информационные выходы 8 устройства, выходы 9 расширения, управляющий вход

10напряжения сдвига, управляющий вход

11расширения, управляющий вход 12 типа сдвига (арифметического или логического), управляющий вход 13 - циклического сдвига, вход 14 старшего (знакового) разряда. В качестве блока 1 циклического сдвига может быть применен любой из известных одно- тактных комбинационных сдвигателей, позволяющих производить циклический сдвиг информации, например, влево.

Входами блока 1 циклического сдвига являются информационные входы 6 устройства и входы 5 параметра сдвига. Выходы 15 блока 1 циклического сдвига являются входами блока 3 формирования результата и блока 4 расширения сдвига.

VJ

О Ю CJ

4D

Формирователь 2 кода маски (фиг. 2) предназначен для выработки корректирующих сигналов и содержит обычный дешифратор 16 с инверсными выходами, входы которого являются входами 5 соответствующих по весу (от 1 до 3) разрядов параметра сдвига и элементы И с весом от 1 до 8, выходы которых являются выходами 17 формирователя 2 кода маски.

Блок 3 формирования результата (фиг. 3) предназначен для окончательного формирования результата сдвига. Он содержит элементы И 18 с весом от 1 до 8, N мультиплексоров 19 первой группы с весом от 1 до 8, мультиплексор 20 и мультиплексоры 21 второй группы с весом от 1 до 8.

Блок 4 расширения сдвига предназначен для формирования выдвигаемой части при арифметических и логических сдвигах, которая выдается по выходам 9 расширения устройства.

Выдвигаемая часть должна храниться в регистре расширения. Это необходимо для выполнения сдвига информации большей разрядности. В качестве регистра расширения может быть использован любой регистр, разрядность которого равна разрядности устройства сдвига информации.

Блок 4 расширения сдвига состоит из элементов И 22 с весом от 1 до 8 и мультиплексоров 23 с весом от 1 до 8.

Устройство для сдвига информации работает следующим образом. Сдвигаемая информация по информационным входам 6 устройства поступает на входы блока 1 циклического сдвига, который осуществляет циклический сдвиг влево на необходимое число разрядов соответственно параметру сдвига, поступающему по управляющим входам 5.

С выходов 15 блока 1 циклического сдвига сдвинутая циклическая информация поступает на входы блока 3 формирования результата и на входы блока 4 расширения сдвига,

Необходимо отметить, что параметр сдвига поступает на входы 5 устройства в инверсном коде и параметр сдвига вправо является дополнением параметра сдвига влево.

Одновременное блоком 1 циклического сдвига работает формирователь 2 кода маски, который на основе поступившей информации по управляющим входам 5 параметра сдвига формирует независимо от направления сдвига код маски следующим образом: параметр сдвига дешифрируется в унитарный код на дешифратор 16 с инверсными выходами и далее появившийся уровень логического 0 на одном из выходов дешифратора 16, рапространяется в сторону младших разрядов на элементах И. Код маски поступает с выходов 17 формирователя 2

кода маски на управляющие входы узла 3 формирования результата и блока 4 расширения сдвига.

Далее на основе результатов работы блока 1 циклического сдвига, формировате0 ля 2 кода маски, управляющих сигналов, поступающих по входам 10, 11, 12, 13, 14 в блоке 3 формирования результата формируется результат сдвига информации следующим образом.

5 Если управляющий вход 13 имеет уровень логической 1, что означает циклический сдвиг, то независимо от управляющих сигналов 10, 11, 12 и сигналов кода маски. поступающих по управляющим входам 17,

0 циклически сдвинутая информация со входов 15, поступающая из блока 1 циклического сдвига, передается через информационные входы Х4 мультиплексоров 21 на информационные выходы 9 уст5 ройства.

Если управляющий вход 13 имеет уровень логического 0, это означает логический сдвиг при поступлении на управляющий вход 12 уровня логического 0 или арифме0 тический сдвиг при поступлении на управ-- ляющий вход 12 уровня логической 1. Направление сдвига задается на управляющем входе 10: уровень логической 1 означает правый сдвиг, уровень логического О

5 означает левый сдвиг.

Результат сдвига при логическом или арифметическом сдвиге формируется следующим образом.

При левом логическом или арифметиче0 ском сдвиге в тех разрядах, в которых соответствующие сигналы по управляющим входам 17 имеют уровень логической 1, сдвинутая на необходимое число разрядов информация со входов 15 передается по

5 информационным входам Х2 мультиплексора 21 на информационные входы 8 устройства, за исключением входа Х2 мультиплексора 21 с весом 8.

На вход Х2 мультиплексора 21 с весом

0 8 с выхода элемента И-ИЛИ 20 при логическом сдвиге поступает сигнал с весом 8 по входам 15, или старший (знаковый) разряд, поступающий по управляющему входу 14, при арифметическом сдвиге.

5В разряды, в которых соответствующие

управляющие сигналы по входам 17 имеют уровень логического 0 при логическом или арифметическоми сдвиге передаются сигналы с выходов элементов И 18 по входам XQ мультиплексоров 21, которые принимают

значение логического 0 при сдвиге без расширения (управляющий вход 11 расширения имеет уровень логического 0) или принимают значение соответствующих разрядов регистра расширения, поступающих по информационным входам 7 расширения, при сдвиге с расширением (управляющий вход 11 расширения имеет уровень логической 1).

При правом логическом или арифметическом сдвиге в тех разрядах.в которых соответствующие управляющие сигналы по входам 17 имеют уровень логического О, сдвинутая на необходимое число разрядов информация со входов 15 передается по информационным входам Х1 мультиплексора 21 на информационные выходы 8 устройства.

В разряды, в которых соответствующие управляющие сигналы по входам 17 имеют уровень логической 1, передаются сигналы с выходов элементов И-ИЛИ 19, которые принимают значение старшего (знакового) разряда, поступающего по управляющему входу 14, при арифметическом сдвиге, или принимают значение сигналов с выходов элементов И 18 при логическом сдвиге. Сигналы на выходах элементов И 18 принимают значение логического 0 при сдвиге без расширения (управляющий вход 11 расширения имеет уровень логического 0 ) или значение соответствующих разрядов регистра расширения, поступающих по информационным входам 7 расширения при сдвиге с расширением (управляющий вход 11 расширения имеет уровень логической

1).

Одновременно с блоком 3 формирования результата работает блок 4 расширения сдвига, который на основе результатов работы блока 1 циклического сдвига и формирователя 2 кода маски, а также с учетом управляющих сигналов, поступающих по входам 10 ,12,13,14 формирует и выдает по информационным выходам 9 расширения устройства выдвигаемую часть при сдвиге следующим образом.

При циклическом сдвиге (управляющий вход 13 имеет уровень логической 1) на информационные выходы 9 расширения устройства передаются сигналы с выходов элементов И 22, принимающие значение логического 0 при циклическом сдвиге, по ин- формационным входам ХО и ХЗ мультиплексоров 23 или передается уровень логического 0 по информационным входам Х1 и Х2 мультиплексоров 23 в зависимости от значения управляющих сигналов кода маски, поступающих на адресные входы А1 мультиплексоров 23 и управляющего

сигнала на входе 10, поступающего на адресные входы АО мультиплексоров 23. Выдвигаемая часть при логическом или арифметическом сдвиге формируется следующим образом. При левом логическом и арифметическом сдвигах в тех разрядах, в которых соответствующие сигналы по управляющим входам 17 имеют уровень логического 0, сдвинутая информация со входов

0 15 через элементы И 22 по информационным входам ХО мультиплексоров 23 передается на информационные выходы 9 расширения устройства, разряды, в которых соответствующие сигналы по управляющим

5 входам 17 имеют уровень логической 1, дополняются нулями с информационных входов Х2 мультиплексоров 23.

При правом логическом и арифметическом сдвигах в тех разрядах, в которых со0 ответствующие сигналы по управляющим входам 17 имеют уровень логической 1, сдвинутая информация со входов 15 через элементы И 22 по информационным входам ХЗ мультиплексоров 23 передается на ин5 формационные выходы 9 расширения устройства, разряды, в которых соответствующие сигналы по управляющим входам 17 имеют уровень логического 0 , дополняются нулями, поступающими по ин0 формационным входам Х1 мультиплексоров 23.

Пусть необходимо логически сдвинуть 16-разрядное информационное слово А (16...1) 1001 1100 1010 111 на 3 разряда

5 влево с помощью 8-разрядного устройства сдвига информации.

Поскольку разрядность сдвигаемой информации в 2 раза больше разрядности устройства, то сдвиг будет осуществляться

0 последовательно в 2 этапа: на 1 этапе будет производиться логический сдвиг без расширения на 3 разряда влево младшего байта информационного слова, на 2 этапе - логический сдвиг на 3 разряда влево с расшире5 нием старшего байта (т.е. освободившиеся разряды старшего байта будут заполняться выдвинутыми на 1 этапе разрядами младшего байта).

На 1 этапе младший байт сдвигаемого

0 информационного слова А(8...1) 10Ю 111 по информационныцм входам 6(8...1) устройства поступает на входы узла 1 циклического сдвига, который осуществляет циклический сдвиг влево на необходимое

5 число разрядов соответственно параметру сдвига 100 поступающему по управляющим входам (3, 2, 1).

С выходов 15 (8...1) узла 1 циклического сдвига сдвинутая циклическая информация А (5... 1, 8...6) 0111 1101 поступает на входы

блока 3 формирования результата и на входы блока 4 расширения сдвига.

Одновременное блоком 1 циклического сдвига работает формирователь 2 кода маски: при поступлении на входы 5 (3, 2, 1) параметра сдвига кода 100 после дешифрации на выходах дешифратора 16(0...6) будет - ставлен следующий код 1111 011, далее нот код корректируется на элементах И соответствующим образом и на выходах 17 (1...8) будет выставлен следующий код маски 0001 111, который поступает на управля- ющие входы блока 3 формирования результата и блока 4 расширения сдвига.

Далее на основе результата работы блока 1 циклического сдвига, формирователя 2 кода маски, управляющих сигналов, поступающих по входам 10, 11, 12, 13, 14 (управляющие сигналы, поступающие по входам 10, 11, 12, 13, имеют уровень логического 0) в блоке 3 формирования результата формируется результат логического сдвига влево младшего байта 0111 1000, который выдается по информационным выходам 8 (8...1) устройства (информация, поступающая по входам 7 расширения из регистра расширения на 1 этапе не учитывается, т.к. производится сдвиг без расширения).

Одновременно с блоком 3 формирования результата сдвига работает узел 4 расширения сдвига, который на основе результата работы блока 1 циклического сдвига и формирователя 2 кода маски, а также с учетом управляющих сигналов, поступающих по входам 10,13 формирует и выдает информационным выходам 9 (8...1) расширения устройства выдвигаемую часть 0000 0101 при выполнении логического сдвига влево младшего байта, предназначенную для хранения в регистре расширения.

На 2 этапе старший байт сдвигаемого информационного слова А (16...9) 1001 1100 по информационным входам 6 (8...1) устройства поступает на входы узла 1 циклического сдвига, аналогично младшему байту сдвигается и с выходов 15 (8...1) узла циклического сдвига код 11100100 поступает на входы блока 3 фомирования результата и на входы блока 4 расширения сдвига. При этом на выходах 17(1 .,.8) формирователя 2 кода маски код маски не меняется.

Далее с учетом циклически сдвинутого старшего байта, поступающего по входам 15 (8...1), кода маски, поступающего по входам 17(8...1), сигналов, поступающих по входам 7 (8...1) расширения из регистра расширения (где хранится выдвинутая часть при сдвиге младшего байта информационного слова на 1 этапе), в блоке 3 формирования результата формируется результат логического сдвига влево старшего байта 1110 0101, который выдается по информационным выходам 8 (8...1) устройства. Причем управляющий вход 11 на 2 этапе имеет уровень логической 1, сигналы по управляющим входам 10, 12, 13 не меняются.

Аналогично 1 этапу в узле 4 расширения сдвига формируется и выдается по инфор0 мационным выходам 9 (8...1) расширения устройства выдвигаемая часть 0000 0100 при выполнении логического сдвига влево старшего байта 16-разрядного информационного слова.

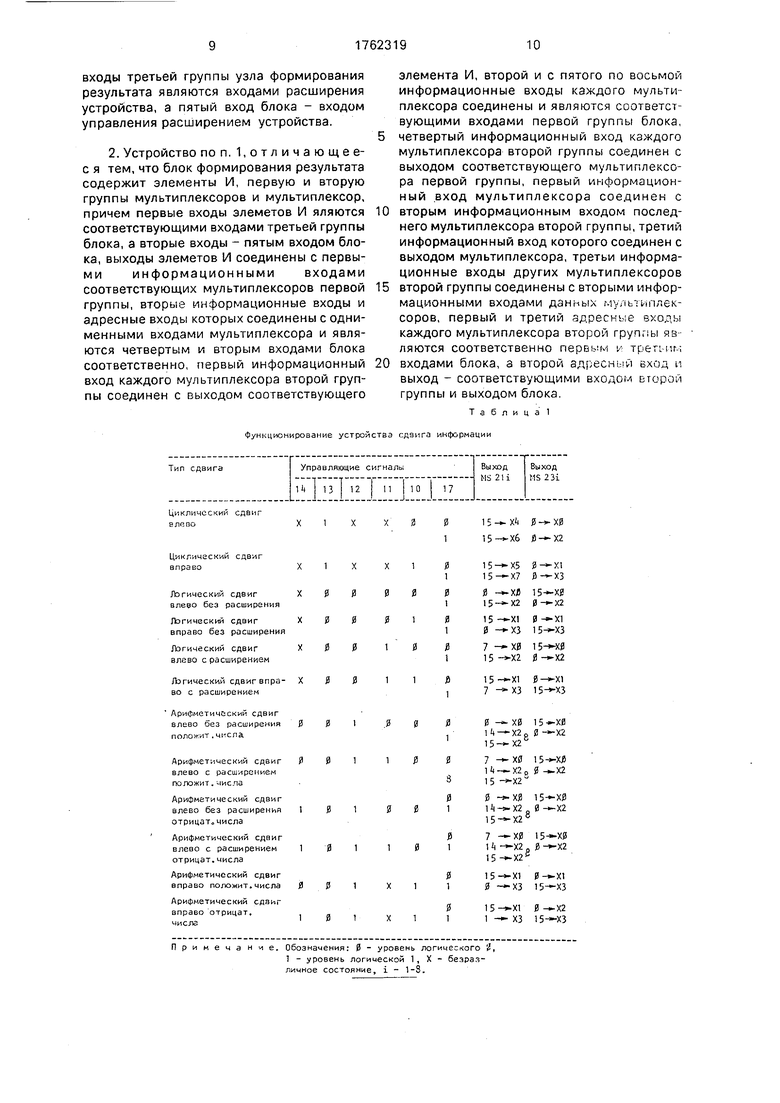

5Функционирование устройства для

сдвига информации при различных типах сдвигов иллюстрируется таблицей функционирования устройства (табл. 1), а последовательность выполнения сдвигов

0 16-разрядной информации поясняется табл. 2.

Формула изобретения 1. Устройство для сдвига информации, содержащее N-разрядный блок циклическо5 го сдвига, входы первой группы которого являются информационными входами устройства, формирователь кода маски, входы которого соединены с входами второй группы блока циклического сдвига и являются

0 входами параметра сдвига устройства, и блок формирования результата, выходы которого являются информационными выходами устройства, входы первой и второй групп соединены соответственно с выхода5 ми блока циклического сдвига и формирователя кода маски, а первый - четвертый входы являются соответственно входами направления сдвига, типа сдвига, циклического сдвига и знакового разряда устройст0 ва, отличающееся тем, что, с целью расширения области применения за счет возможности сдвига информации, разрядность которой кратна N. в устройство введен блок расширения сдвига информации,

5 состоящий из N элементов И и N мультиплексоров, причем первые входы элементов И соединены с соответствующими выходами блока циклического сдвига, а вторые входы - с третьим входом блока формирования

0 результата, выходы элементов И соединены с первыми и четвертыми информационными входами соответствующих мультиплексоров, вторые и третьи входы которых являются входом логического нуля устройства,

5 адресные входы первой группы соединены с первым входом блока формирования результата, а адресные входы второй группы - с соответствующими выходами формирователя маски, выходы мультиплексоров являются выходами расширения устройства,

входы третьей группы узла формирования результата являются входами расширения устройства, а пятый вход блока - входом управления расширением устройства.

2. Устройство по п. 1,отличающее- с я тем, что блок формирования результата содержит элементы И, первую и вторую группы мультиплексоров и мультиплексор, причем первые входы элеметов И яляются соответствующими входами третьей группы блока, а вторые входы - пятым входом блока, выходы элеметов И соединены с первыми информационными входами соответствующих мультиплексоров первой группы, вторые информационные входы и адресные входы которых соединены с одни- менными входами мультиплексора и являются четвертым и вторым входами блока соответственно, первый информационный вход каждого мультиплексора второй группы соединен с выходом соответствующего

элемента И, второй и с пятого по восьмой информационные входы каждого мультиплексора соединены и являются соответствующими входами первой группы блока

четвертый информационный вход каждого мультиплексора второй группы соединен с выходом соответствующего мультиплексора первой группы, первый информационный вход мультиплексора соединен с

вторым информационным входом последнего мультиплексора второй группы, третий информационный вход которого соединен с выходом мультиплексора, третьи информационные входы других мультиплексоров

второй группы соединены с вторыми информационными входами данпых .- соров, первый и третий здреоч е вхолы каждого мультиплексора второй груп,,ы яз ляются соответственно первом i/ тсепиг,

входами блока, а второй ад,есн и вход и выход - соответствующими входом Б торой группы и выходом блока

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1580368A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| Устройство для сдвига операндов | 1987 |

|

SU1481741A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Устройство для сдвига информации | 1986 |

|

SU1363310A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297116A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных системах обработки информации. Цель изобретения - расширение области применения устройства за счет возможности выполнения сдвига информации, разрядность которой кратна N (N -- разрядность устройства). Поставленная цель достигается вводом в устройство но - вого блока - блока расширения сдвига, предназначенного для формирования выдвигаемой части информации при арифметических и логических сдвигах, что необходимо для выполнения сдвигов информации большей разрядности, чем разрядность устройства, а также для возможности организации аппаратного контроля выполнения операции сдвига. Использование свойства зеркальности правого сдвига относительно левого позволяет построить узел формирования кода маски без зеркальной перестановки разрядов при формировании кода маски, что приводит к упрощению устройства. 1 з.п. ф-лы, 2 табл., 4 ил.

Функционирование устройства сдвига информации

Uk клическии сдвиг

Примечание. Обозначения: 0 - уровень логического t, 1 - уровень логической 1, X - безразличное состояние, i - 1-S.

Таблица2

Последовательность функционирования устройства сдвига информации при выполнении сдвигов 16-разрядной информации

Фиг.З

1р я

| Устройство сдвига | 1979 |

|

SU809387A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № 1171851,кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-09-15—Публикация

1989-01-04—Подача