Изобретение относится к области автоматики и вычислительной техники и может быть использовано при проектировании микропрограммных устройств управления.

Целью изобретения является сокращение объема оборудования микропрограммного устройства управления за счет повышения гибкости адресации микрокоманд.

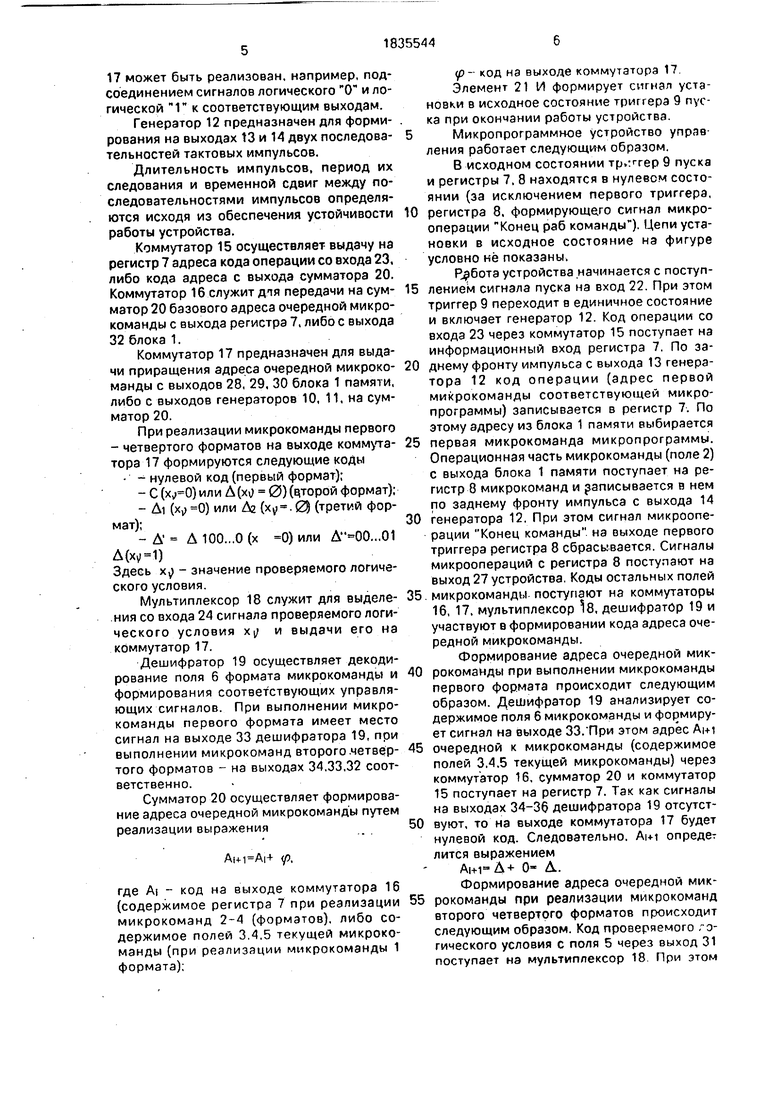

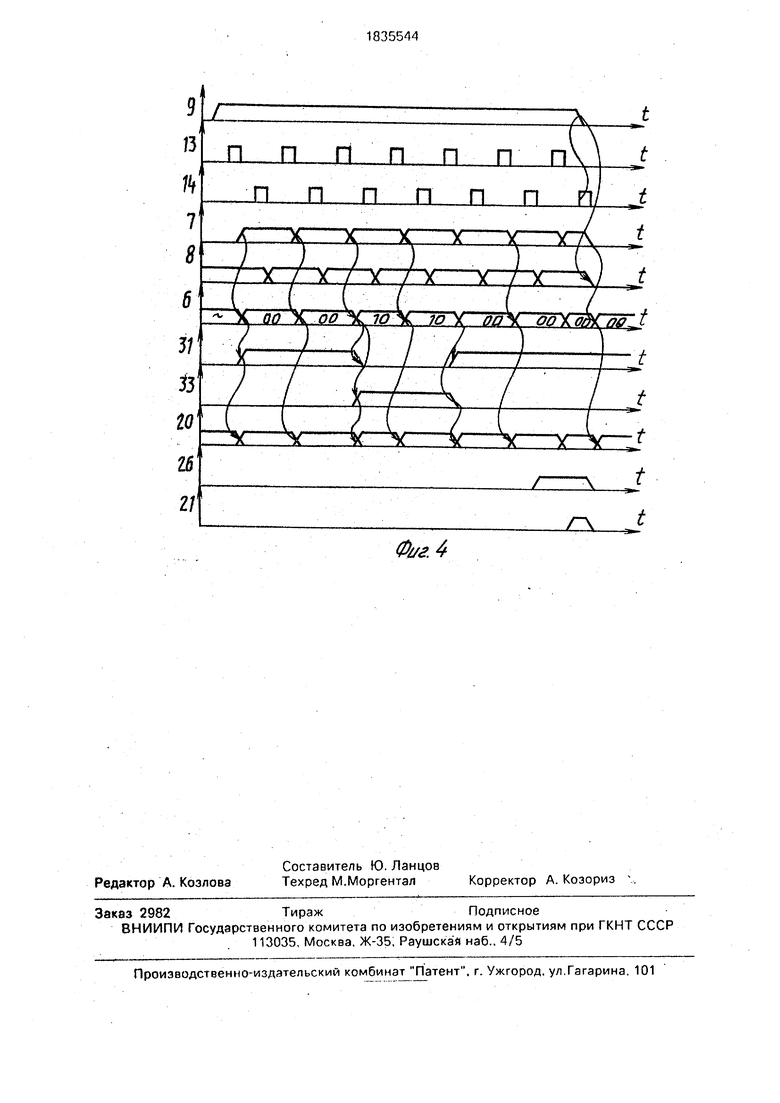

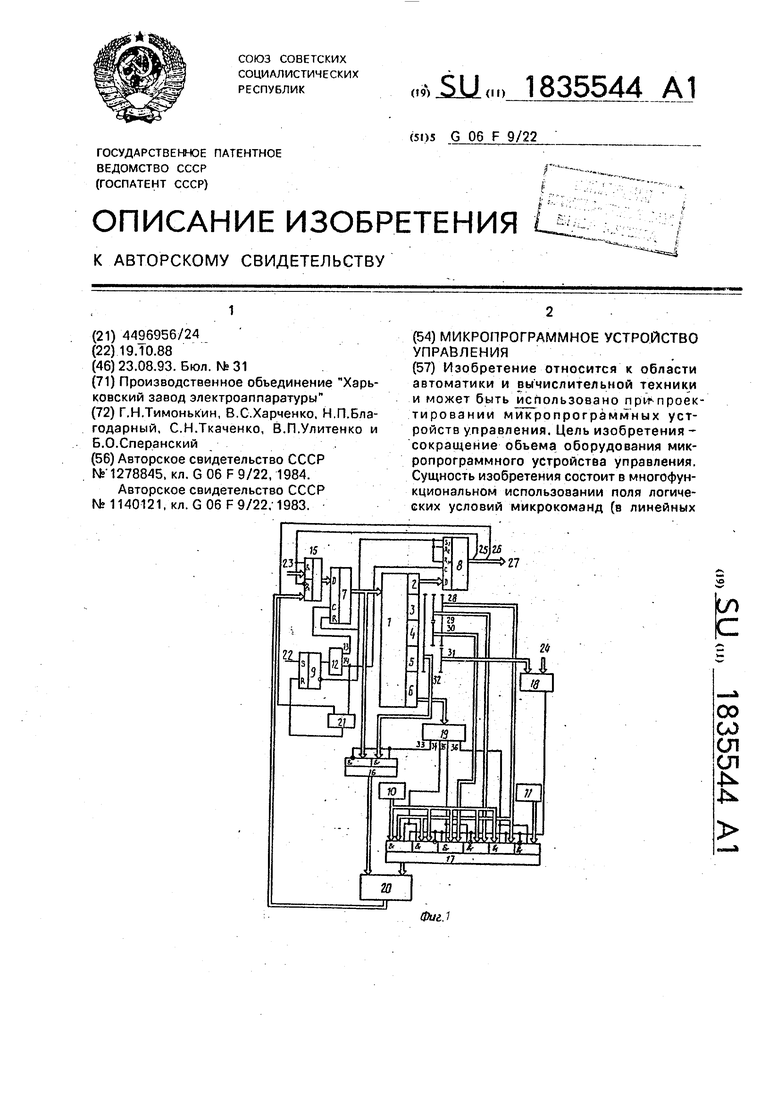

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг.2 - форматы микрокоманд; на фиг.З - размещение микрокоманд- последователей в блоке памяти; на фиг.4 - временная диаграмма работы устройства.

Микропрограммное устройство управления, (фиг. 1) содержит блок 1 памяти с выходами 2 поля микроопераций, первого и второго полей 3, 4, адреса поля 5 кода условия, поля 6 типа адресации, регистр 7 адреса, регистр 8 микрокоманд, триггер 9 пуска, генератор 10 константы, генератор 11 константы, генератор 12 импульсов с выходами 13 (первой последовательности импульсов) и 14 (второй последовательности импульсов), первый коммутатор 15 адреса, второй

16коммутатор адреса, Третий коммутатор

17адреса, мультиплексор 18, дешифратор 19,сумматор 20, элемент 21 И, вход 22 пуска, вход 23 кода операции, вход 24 условий, выход 25 сигнала микрооперации Конец команды, выход 2.6 сигнала микрооперации Конец работы, выходы 27 микроопераций, выходы 28 первого и второго полей адреса, выход 29 первого поля адреса, выход 30 второго поля адреса, выход 31 поля кода условия, выход 32 первого и второго полей адреса и поля кода условия, выходы 33-36 дешифратора 19.

Назначение элементов и узлов устройства.

Блок 1 памяти предназначен для хранения микрокоманд. В устройстве реализуется четыре формата микрокоманд (фиг.2):

-первый формат (фиг.2,а) - в полях 3-5 микрокоманды записан адрес АСл следующей микрокоманды, в поле 2 -- код микроопераций, в поле 6 - код 00;

- второй формат (фиг.26) - полях 3. 4

микрокоманды записан код А приращения адреса, в поле 5 - код логического условия, в поле 2 - код микроопераций, в поле 6 - код 01;

- третий формат - в поле 3 записан код Д1 первого приращения, в поле 4 записан код Дг второго приращения, в поле 5 записан код логического условия, в поле-код 10;

-четвертый формат - в поле 3 записан код AI первого приращения, в поле 4 запи:

сан код Д второго приращения, в поле 5 код логического условия, в поле 6 - код 11.

Содержимое полей 3,4,5 поступает на

выход 32, содержимое полей 3, 4 поступает

на выход 28, содержимое полей 3 и 4 поступает соответственно на выходы 29, 30.

Регистр 7 служит для хранения адреса микрокоманды и выдачи его на блок 1 памяти.

Регистр 8 предназначен для хранения содержимого поля 2 микроопераций микрокоманд и выдачи его на выходы 25, 26, 27. В исходном состоянии все триггеры регистра 8 за исключением триггера соответствующего сигналу микрооперации Конец команды, находятся в нулевом состоянии.

Триггер 9 пуска служит для включения генератора 12 импульсов и установки в исходное состояние регистров 7,8. При нахождении триггера 9 в единичном состоянии включен генератор 12. При нахождении триггера 9. в нулевом состоянии генератор 12.. выключен и регистры 7,8 находятся в исходном состоянии,

Генератор 10 формирует нулевой код и выдает его на соответствующие входы коммутатора 17.

Генератор.11 формирует ко константы С и выдает его на коммутатор 17. Генератор

17 может быть реализован, например, подсоединением сигналов логического О и логической 1 к соответствующим выходам.

Генератор 12 предназначен для формирования на выходах t3 и 14 двух последовательностей тактовых импульсов.

Длительность импульсов, период их следования и временной сдвиг между последовательностями импульсов определяются исходя из обеспечения устойчивости работы устройства.

Коммутатор 15 осуществляет выдачу на регистр 7 адреса кода операции со входа 23, либо кода адреса с выхода сумматора 20. Коммутатор 16 служит для передачи на сумматор 20 базового адреса очередной микрокоманды с выхода регистра 7, либо с выхода 32 блока 1.

Коммутатор 17 предназначен для выдачи приращения адреса очередной микрокоманды с выходов 28, 29, 30 блока 1 памяти, либо с выходов генераторов 10, 11, на сумматор 20.

При реализации микрокоманды первого - четвертого форматов на выходе коммутатора 17 формируются следующие коды - - нулевой код (первый формат);

-С ()или Д(х 0)(в,торой формат);

-Д1 () или Дг (ху .{2§ (третий формат);

-Л1 « Л 100...О (х 0) или Д НЭО.,,01 Л(ху-1)

Здесь х) - значение проверяемого логического условия.

Мультиплексор 18 служит для выделения со входа 24 сигнала проверяемого логического условия х и выдачи его на коммутатор 17.

Дешифратор 19 осуществляет декодирование поля 6 формата микрокоманды и формирования соответствующих управляющих сигналов. При выполнении микрокоманды первого формата имеет место сигнал на выходе 33 дешифратора 19, при выполнении микрокоманд второго .четвертого форматов - на выходах 34,33,32 соответственно.

Сумматор 20 осуществляет формирование адреса очередной микрокоманды путем реализации выражения

р,

где AI - код на выходе коммутатора 16 (содержимое регистра 7 при реализации микрокоманд 2-4 (форматов), либо содержимое полей 3.4.5 текущей микрокоманды (при реализации микрокоманды 1 формата);

р код на выходе коммутатора 17. Элемент 21 И формирует сигнал установки в исходное состояние триггера 9 пуска при окончании работы устройства. 5Микропрограммное устройство управления работает следующим образом.

В исходном состоянии триггер 9 пуска и регистры 7, 8 находятся в нулевом состоянии (за исключением первого триггера,

0 регистра 8. формирующего сигнал микрооперации Конец раб команды). Цепи установки в исходное состояние на фигуре условно не показаны.

Работа устройства начинается с поступ5 лением сигнала пуска на вход 22. При этом триггер 9 переходит в единичное состояние и включает генератор 12. Код операции со входа 23 через коммутатор 15 поступает на информационный вход регистра 7, По за0 днему фронту импульса с выхода 13 генератора 12 код операции (адрес первой микрокоманды соответствующей микропрограммы) записывается в регистр 7. По этому адресу из блока 1 памяти выбирается

5 первая микрокоманда микропрограммы. Операционная часть микрокоманды (поле 2) с выхода блока 1 памяти поступает на регистр 8 микрокоманд и записывается в нем по заднему фронту импульса с выхода 14

0 генератора 12. При этом сигнал микрооперации Конец команды, на выходе первого триггера регистра 8 сбрасывается. Сигналы микроопераций с регистра 8 поступают на выход 27 устройства. Коды остальных полей

5. микрокоманды поступают на коммутаторы 16, 17, мультиплексор 18, дешифратор 19 и участвуют в формировании кода адреса очередной микрокоманды.

Формирование адреса очередной мик0 рокоманды при выполнении микрокоманды первого формата происходит следующим образом. Дешифратор 19 анализирует содержимое поля б микрокоманды и формирует сигнал на выходе 33. При этом адрес AI-H

5 очередной к микрокоманды (содержимое полей 3.4,5 текущей микрокоманды) через коммутатор 16, сумматор 20 и коммутатор 15 поступает на регистр 7. Так как сигналы на выходах 34-36 дешифратора 19 отсутст0 вуют, то на выходе коммутатора 17 будет нулевой код. Следовательно. Ai+t опредет лится выражением Ам Д + О- Д. Формирование адреса очередной мик5 рокоманды при реализации микрокоманд второго четвертого форматов происходит следующим образом. Код проверяемого логического условия с поля 5 через выход 31 поступает на мультиплексор 18 При этом

проверяемое логическое условие х со входа 24 поступают через мультиплексор 18 на коммутатор 17.

При выполнении микрокоманды второго формата сигнал будет на выходе 34 дешифратора 19, В этом случае на выход коммутатора 17 передается код с выхода генератора 11 константы (при хуО) либо код с выхода 28 блока 1 памяти (при хд 1) и адрес Ац-1 очередной микрокоманды на выходе сумматора 20 формируется в соответствии со следующим выражением AI+C, при х $ 0

AI-H- |

Ан-д , при

При выполнении микрокоманд третьего формата сигнал будет на выходе 33 дешифратора 19. В этом случае на выход коммутатора 17 передается код AI с выхода 29 блока 1 памяти (при хя-0), либо код Дг с выхода 30 блока 1 памяти (при ). Адрес Аьм очередной микрокоманды в этом случае определяется выражением

AI+ Дь при ,

AI+I-

AI+ Дг, при .

При выполнении микрокоманд четвертого формата сигнал будет на выходе 32 дешифратора 19. В этом случае на выход коммутатора 17 передается код 0001 Д(при ) либо код Д100...0(при ). Адрес Аи-1 очередной микрокоманды в этом случае определяется выражением

Ai+0001 Д. прих,,0, г.

Ан-i |

AI+ А 100....О, .

Сформированный адрес Ан-i (для всех типов форматов микрокоманд) с выхода сумматора 20 через коммутатор 15 поступает на регистр 7. По очередному импульсу с выхода 13 генератора 12 адрес Ai+i записывается в регистр 7. По этому адресу из блока 1 памяти выбирается очередная микрокоманда. Далее устройство функционирует аналогично описанному выше алгоритму.

Формула изобретения

Микропрограммное устройство управления, содержащее блок памяти, регистр адреса, регистр микрокоманд, первый коммутатор адреса, триггер пуска, мультиплексор, генератор импульсов, причем вход кода операции устройства соединен с первым информационным входом первого коммутатора адреса, выход которого соединен с информационным входом регистра адреса. выход регистра адреса соединен г адресным входом блока памяти, выход попп микроопераций блока памяти соединен с информационным входом регистра микрокоманд, выходы микрооперации которого соединены с выходами микроопераций устройства, выход признака Конец команды регистра микрокоманд соединен с управляющим входом первого коммутатора адреса, вход пуска устройства соединен с установочным входом триггера пуска, прямой вы0 ход которого соединен с входом пуска генератора импульсов, первый и второй выходы которого соединены с входами синхронизации соответственно регистра адреса и регистра микрокоманд, выход поля кода ус5 ловия блока памяти соединен с адресным входом мультиплексора, информационные входы которого подключены к входам условий устройства, отличающееся тем, что, с целью сокращения объема оборудова0 ния, оно содержит первый и второй генераторы константы/ второй и третий коммутаторы адреса, дешифратор, сумматор и элемент И, причем выход регистра адреса соединен с первым информацион5 ным входом второго коммутатора адреса, выход которого соединен с первым входом сумматора, выход которого соединен с вторым информационным входом первого ком; мутатора адреса, выходы первого и второго

0 полей адреса и поля кода условия блока памяти соединены с вторым информационным входом второго коммутатора адреса, выход первого генератора константы соединен с первым информационным входом

5 третьего коммутатора адреса, выход первого и второго полей адреса блока памяти соединен с вторым информационным входом третьего коммутатора адреса, выход первого поля адреса блока памяти соединен с

0 третьим информационным входом третьего коммутатора адреса, четвертый информационный вход которого соединен с выходом второго поля адреса блока памяти, выход второго генератора константы соединен с

5 пятым информационным входом третьего коммутатора адреса, выход которого соединен с вторым входом сумматора, выход поля типа адресации блока памяти соединен с входом дешифратора, первый выход де0 шифратора соединен с управляющим входом второго коммутатора адреса, с второго по четвертый выходы дешифратора соединены соответственно с первого по третий управляющими входами третьего коммута5 тора адреса, выход мультиплексора соединен с четвертым управляющим входом третьего коммутатора адреса, второй выход генератора импульсов соединен с первым входом элемента И. выход которого соединен С ВХОДОМ сбрПГс Триггеру пуска, ВЫХОД

признака Конец работы регистра микро- нен с-входом сброса регистра адреса и уста- команд соединен с вторым входом элемента новочными входами соответствующих раз- И. инверсный выход триггера пуска соеди- рядов регистра микрокоманд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при -проектировании микропрограммных устройств управления. Цель изобретения - сокращение объема оборудования микропрограммного устройства управления. Сущность изобретения состоит в многофункциональном использовании поля логических условий микрокоманд (в линейных

а)

6)

Фиг.

6)

РигЭ

& .А1(00...0) й(00...0)/й

П П П П П П П

П П П П П ПП1

i

Ж X X X

7)Г

У

х Ч/

zx

t

t

х Ч/ J

zx

0Ј/.4

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1278845A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

Авторы

Даты

1993-08-23—Публикация

1988-10-19—Подача