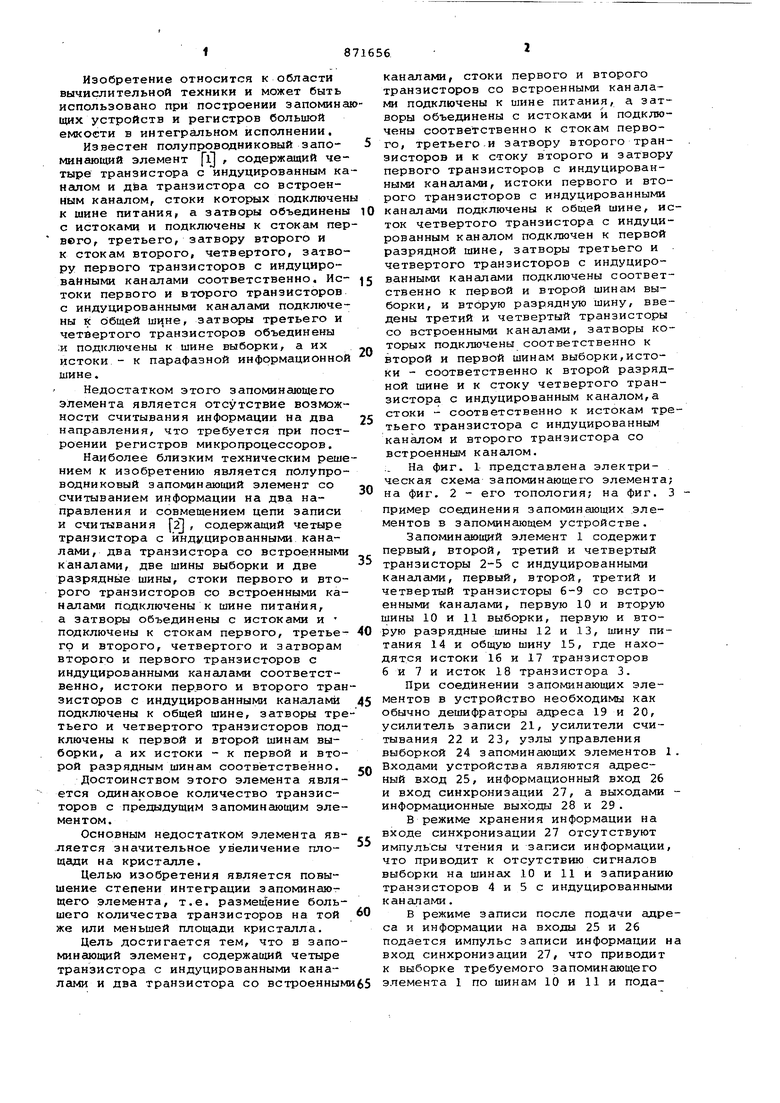

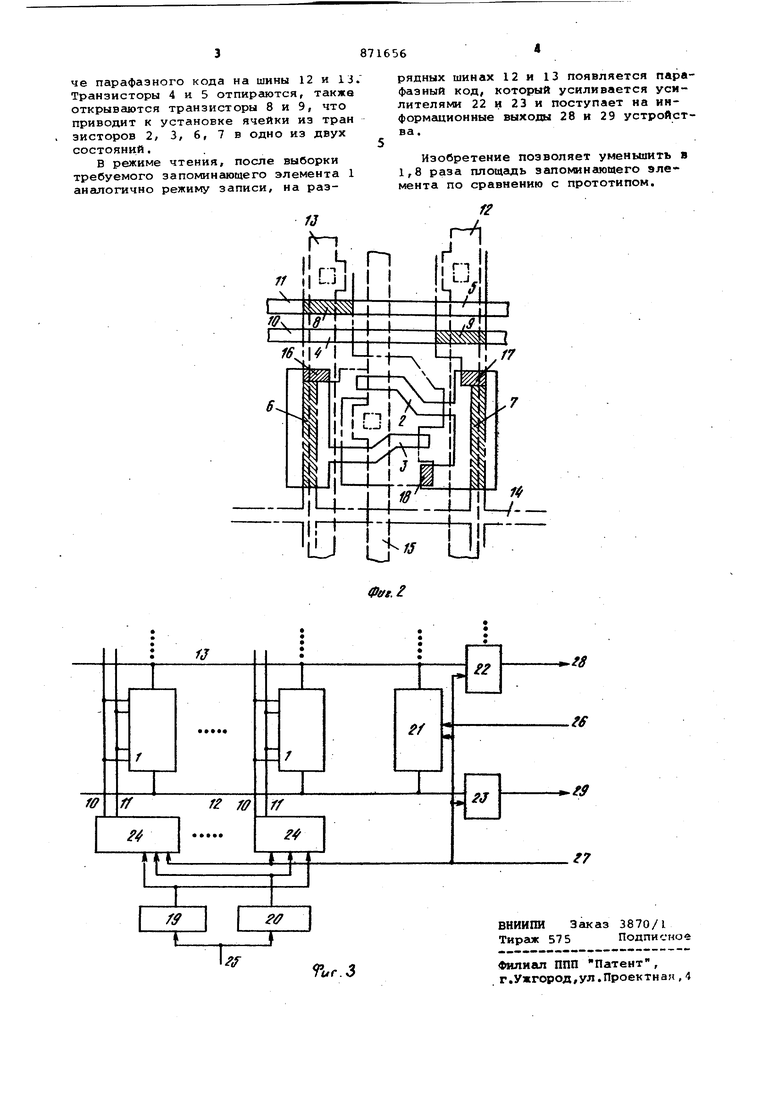

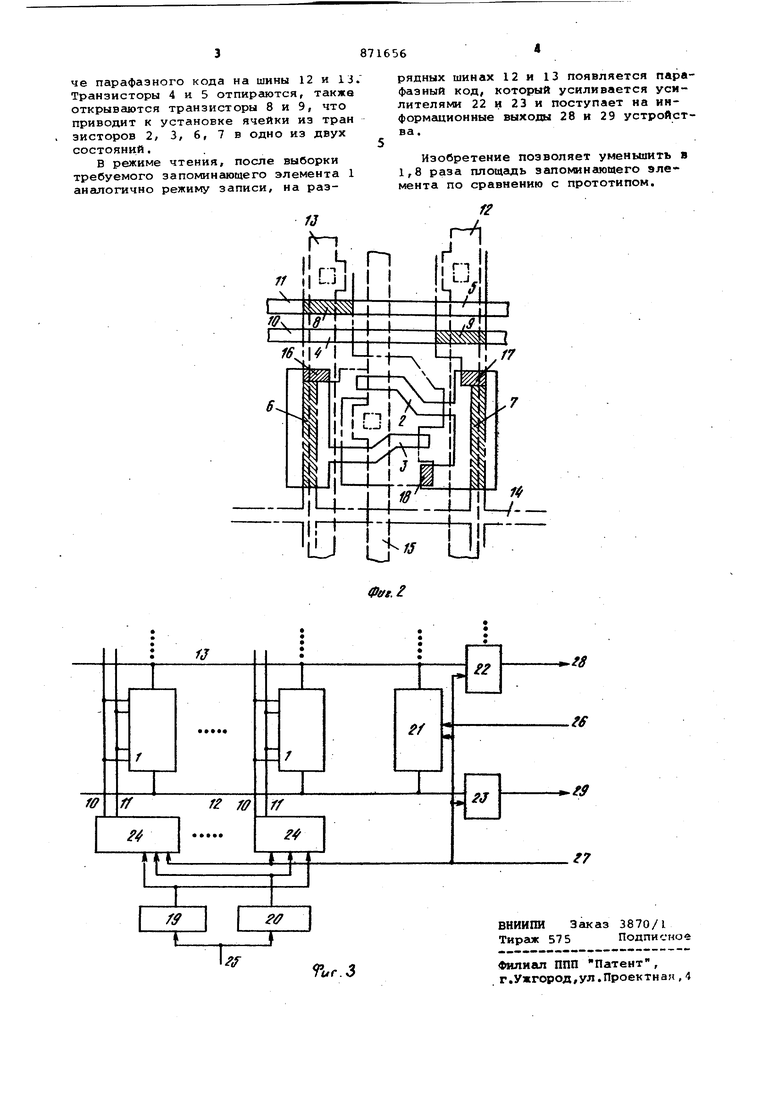

Изобретение относится к области вычислительной техники и может быть использовано при построении запомин щих устройств и регистров большой емкости в интегральном исполнении. Известен полупроводниковый эапоминающий элемент fl , содержащий че тыре транзистора с индуцированным к налом и два транзистора со встроенным каналом, стоки которых подключе к шине питания, а затворы объединен с истоками и подключены к стокам пе вего, третьего, затвору второго и к стокам второго, четвертого, затво ру первого транзисторов с индуцированными каналами соответственно, Ис токи первого и второго транзисторов с индуцированными канашами подключе ны к Ьбщей шине, затворы третьего и четвертого транзисторов объединены :и подключены к шине выборки, а их истоки - к парафазной информационно шине. Недостатком этого запоминающего элемента является отсутствие возмож ности считывания информации на два направления, что требуется при пост роении регистров микропроцессоров. Наиболее близким техническим реш нием к изобретению является полупро водниковый запоминающий элемент со считыванием информации на два направления и совмещением цепи записи и считывания 2 , содержащий четыре транзистора с индуцированными каналами, два транзистора со встроенными каналами, две шины выборки и две разрядные шины, стоки первого и вто рого транзисторов со встроенными каналами подключены к шине питания, а затворы объединены с истоками и подключены к стокам первого, третье гр и второго, четвертого и затворам второго и первого транзисторов с индуцированными каналами соответственно, истоки перового и второго тран зисторов с индуцированными каналами подключены к общей шине, затворы тре тьего и четвертого транзисторов подключены к первой и второй шинам выборки, а их истоки - к первой и второй разрядным шинам соответственно. Достоинством этого элемента является одинаковое количество транзисторов с предыдущим запоминающим элементом. Основным недостатком элемента является значительное увеличение площади на кристалле. Целью изобретения является повышение степени интеграции запоминающего элемента, т.е. размет ение большего количества транзисторов на той же или меньшей площади кристалла. Цель достигается тем, что в запоминёиощий элемент, содержащий четыре транзистора с индуцированными каналами и два транзистора со встроенным каналами, стоки первого и второго транзисторов со встроенными каналами подключены к шине питания, а затворы объединены с истоками и подключены соответственно к стокам первого, третьего и затвору второго транзисторов и к стоку второго и затвору первого транзисторов с индуцированными каналами, истоки первого и второго транзисторов с индуцированными каналами подключены к общей шине, исток четвертого транзистора с индуцированным каналом подключен к первой разрядной шине, затворы третьего и четвертого транзисторов с индуцированными каналами подключены соответственно к первой и второй шинам выборки, и вторую разрядную шину, введены третий и четвертый транзисторы со встроенными каналами, затворы которых подключены соответственно к второй и первой шинам выборки,истоки - соответственно к второй разрядной шине и к стоку четвертого транзистора с индуцированным каналом,а стоки - соответственно к истокам третьего транзистора с индуцированным каналом и второго транзистора со встроенным каналом. :. На фиг. 1 представлена электрическая схема запоминающего элемента; на фиг. 2 - его топология; на фиг. 3 пример соединения запоминающих элементов в запоминающем устройстве. Запоминающий элемент 1 содержит первый, второй, третий и четвертый транзисторы 2-5 с индуцированными каналами, первый, второй, третий и четвертый транзисторы 6-9 со встроенными Каналами, первую 10 и вторую шины 10 и И выборки, первую и вторую разрядные шины 12 и 13, шину питания 14 и общую шину 15, где находятся истоки 16 и 17 транзисторов 6 и 7 и исток 18 транзистора 3. При соединении запоминающих элементов в устройство необходимы как обычно дешифраторы адреса 19 и 20, усилитель записи 21, усилители считывания 22 и 23, узлы управления выборкой 24 запоминающих элементов 1. Входами устройства являются ащресный вход 25, информационный вход 26 и вход синхронизации 27, а выходами информационные выходы 28 и 29. В режиме хранения информации на входе синхронизации 27 отсутствуют импульсы чтения и записи информащии, что приводит к отсутствию сигналов выборки на шинах 10 и 11 и запиранию транзисторов 4 и 5 с индуцированными каналами. В режиме записи после подачи адреса и информации на входы 25 и 26 подается импульс записи информации на вход синхронизации 27, что приводит к выборке требуемого запоминающего элемента 1 по шинам 10 и 11 и подаче парафаэного кода на шины 12 и 1J. Транзисторы 4 и 5 отпираются, также открываются транзисторы 8 и 9, что приводит к установке ячейки из тран зисторов 2, 3, 6, 7 в одно из двух состояний. в режиме чтения, после выборки требуемого запоминающего элемента 1 аналогично режиму записи, на разI h П tiJ рядных шинах 12 и 13 появляется парафазный код, который усиливается усилителями 22 и 23 и поступает на информационные выходы 28 и 29 устройства. Изобретение позволяет уменьшить в 1,8 раза площадь запоминающего элемента по сравнению с прототипом. LIJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Программируемый элемент памяти | 1977 |

|

SU649035A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Ячейка фоточувствительного матричного запоминающего устройства | 1989 |

|

SU1709392A1 |

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Устройство для записи информации в МДП динамический-матричный накопитель | 1982 |

|

SU1091222A1 |

| Элемент памяти | 1988 |

|

SU1594604A1 |

ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ, содержа1ций чезире транзистора с индуцированныко канапакв и два транзистора со встроенными каналами, стоки первого и второго транзисторов со встроенными каналами подключены к шине питания, а затворы объединены с истокдао и подключены соответственно к стокам первого, третьего и затвсфу второго транзисторов и к стоку второго и затвору первого транзисторов с индуцированными каналами, истоки первого и второго транзисторов с индуцированныкм каналами подключены к общей шине, исток четвертого транзистора с индуцированным каналом подключен к первой разрядной шине, затворы третьего и четвертого транзисторов с индуцированными каналами подключены соответственно к первой и второй шинам выборки, и вторую разрядную шину, отличающийся тем, что, с целью повышения степени интеграции элемента, в него введены третий и четвертый транзисторы со встроенными каналами, затворы которых подключены соответственно к второй и первой шинам выборки, истоки соответственно к второй разрядкой шине и к стоку четвертого транзистора с индуцированным каналом, а стоки соответственно к истокам третьего транзистора с индуцированным каналом| и второго транзистора со встроенным каналом. 00 О5 ел О}

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ж | |||

| Электроника, М., Мир, 1977, т | |||

| Способ очищения сернокислого глинозема от железа | 1920 |

|

SU47A1 |

| Пишущая машина | 1922 |

|

SU37A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ гибридной реваскуляризации при многоуровневом поражении брахиоцефальных артерий | 2021 |

|

RU2786008C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-05-07—Публикация

1980-03-31—Подача