Изобретение относится к области вычислительной техники, автоматики и может использоваться в различных цифровых структурах и системах автоматического управления, передачи информации и т.п.

В различных вычислительных и управляющих системах широко используются дешифраторы, реализованные на основе транзисторно-транзисторной и эмиттерно-связанной логики [1-9], работающие по законам булевой алгебры и имеющие по выходу два логических состояния «0» и «1», характеризующихся низким и высоким потенциалами. Классическая архитектура дешифратора опубликована в статьях и книгах [10, 11], серийно выпускаются микросхемы [12].

В работах [13-14], а также монографиях соавтора настоящей заявки [15-16] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с двузначным и многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока I0. Заявляемое устройство «Дешифратор 2 в 4» относится к этому типу логических устройств и работает с входными токовыми сигналами и формирует выходной токовый сигнал.

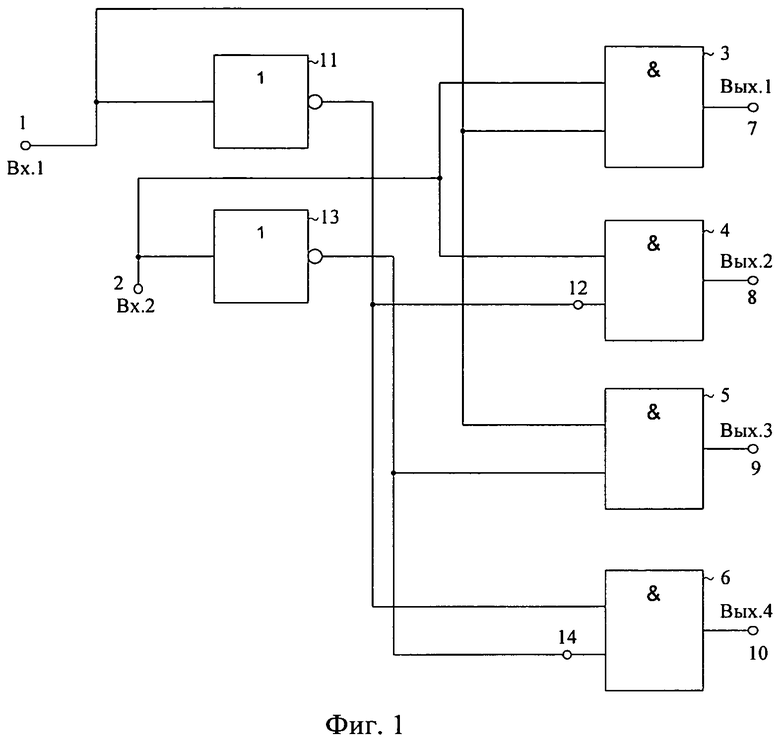

Ближайшим прототипом заявляемого устройства является устройство «Дешифратор 2 в 4», представленный в патенте US 6243319 B1, fig.13, содержащий первый (1) и второй (2) входы устройства, первый (3), второй (4), третий (5) и четвертый (6) логические элементы «2И», выход первого (3) логического элемента «2И» соединен с первым (7) логическим выходом устройства, выход второго (4) логического элемента «2И» соединен со вторым (8) логическим выходом устройства, выход третьего (5) логического элемента «2И» соединен с третьим (9) логическим выходом устройства, выход четвертого (6) логического элемента «2И» соединен с четвертым (10) логическим выходом устройства, первый (11) логический элемент «НЕ», выход которого связан с первым (12) входом второго (4) логического элемента «2И», второй (13) логический элемент «НЕ», выход которого соединен с первым (14) входом четвертого (6) логического элемента «2И».

Существенный недостаток известного устройства «Дешифратор 2 в 4» состоит в том, что его логические элементы, используя потенциальные двоичные сигналы, обладают многоярусной структурой, которую невозможно или неэффективно использовать на современных низковольтных техпроцессах, нелинейностью рабочих режимов элементов и критичностью параметров структуры логических элементов и входных сигналов, что в конечном итоге приводит к снижению быстродействия устройства.

Основная задача предлагаемого изобретения состоит в создании устройства «Дешифратор 2 в 4», в котором внутреннее преобразование информации производится в двузначной токовой форме сигналов, определяемое состоянием входных двоичных токовых сигналов. В конечном итоге это позволяет повысить быстродействие и реализовать устройство на базе современных низковольтных техпроцессов, работающих на принципах линейной алгебры [15-16].

Поставленная задача решается тем, что в логическом устройстве «Дешифратор 2 в 4» (фиг.1), содержащем первый (1) и второй (2) входы устройства, первый (3), второй (4), третий (5) и четвертый (6) логические элементы «2И», выход первого (3) логического элемента «2И» соединен с первым (7) логическим выходом устройства, выход второго (4) логического элемента «2И» соединен со вторым (8) логическим выходом устройства, выход третьего (5) логического элемента «2И» соединен с третьим (9) логическим выходом устройства, выход четвертого (6) логического элемента «2И» соединен с четвертым (10) логическим выходом устройства, первый (11) логический элемент «НЕ», выход которого связан с первым (12) входом второго (4) логического элемента «2И», второй (13) логический элемент «НЕ», выход которого соединен с первым (14) входом четвертого (6) логического элемента «2И», предусмотрены новые элементы и связи - введены первый (15) и второй (16) дополнительные логические элементы «НЕ», выход первого (15) дополнительного логического элемента «НЕ» соединен со вторым (17) входом четвертого (6) логического элемента «2И», выход второго (16) дополнительного логического элемента «НЕ» связан с первым (18) входом третьего (5) логического элемента «2И», причем первый (1) вход устройства связан со входом (19) первого (20) дополнительного размножителя сигнала, первый (21) выход первого (20) дополнительного размножителя сигнала соединен со вторым (22) входом третьего (5) логического элемента «2И», второй (23) выход первого (20) дополнительного размножителя сигнала соединен с первым (24) входом первого (3) логического элемента «2И», третий (25) выход первого (20) дополнительного размножителя сигнала соединен со входом первого (11) логического элемента «НЕ», четвертый (26) выход первого (20) дополнительного размножителя сигнала связан со входом первого (15) дополнительного логического элемента «НЕ», второй (2) вход устройства связан со входом (27) второго (28) дополнительного размножителя сигнала, первый (29) выход второго (28) дополнительного размножителя сигнала соединен со вторым (30) входом первого (3) логического элемента «2И», второй (31) выход второго (28) дополнительного размножителя сигнала соединен со вторым (32) входом второго (4) логического элемента «2И», третий (33) выход второго (28) дополнительного размножителя сигнала соединен со входом второго (16) дополнительного логического элемента «НЕ», четвертый (34) выход второго (28) дополнительного размножителя сигнала связан со входом второго (13) логического элемента «НЕ».

Схема логического устройства «Дешифратор 2 в 4»-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с пп.1-4 формулы изобретения.

На фиг.3 показана схема первого 20 и второго 28 дополнительных размножителей сигналов, которые используются в схеме фиг.2 в соответствии с п.2 формулы изобретения

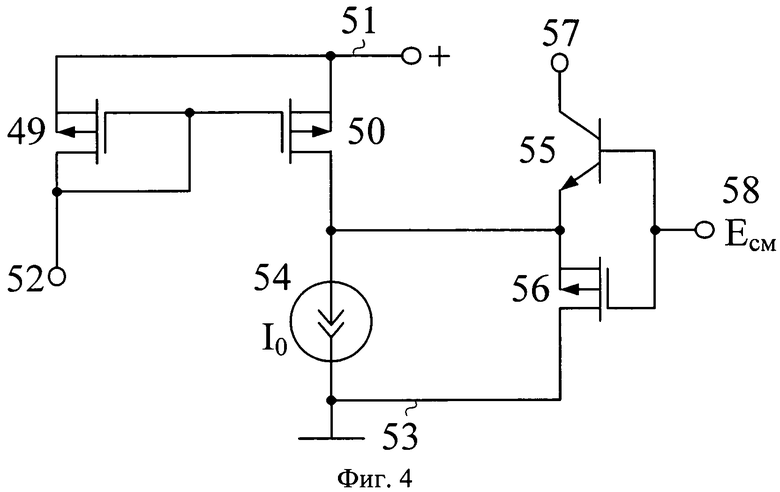

На фиг.4 приведена схема логического элемента «НЕ», который используется в схеме фиг.2 по п.3 формулы изобретения.

На фиг.5 приведена схема логического элемента «2И», который используется в схеме фиг.2 по п.4 формулы изобретения.

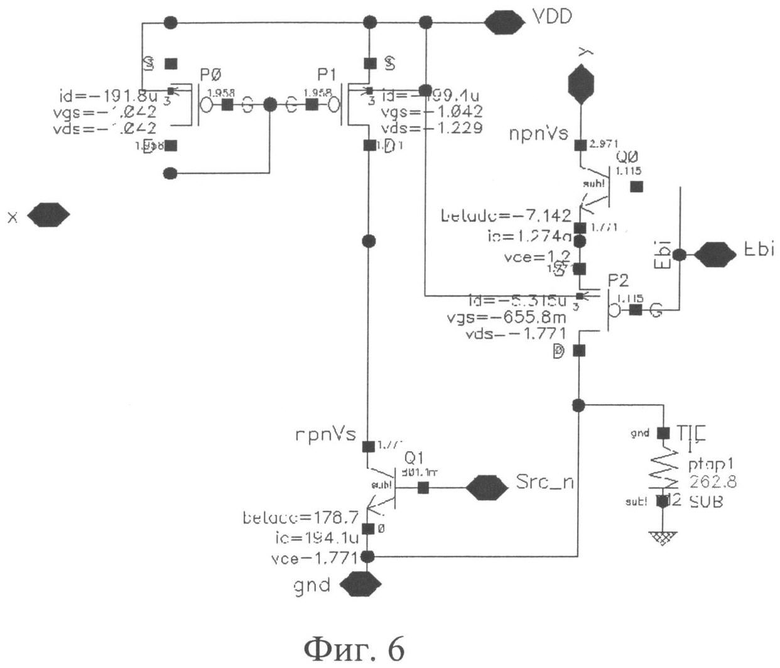

На фиг.6 приведена схема логического элемента «НЕ» в среде компьютерного моделирования Cadence на моделях SiGe транзисторов.

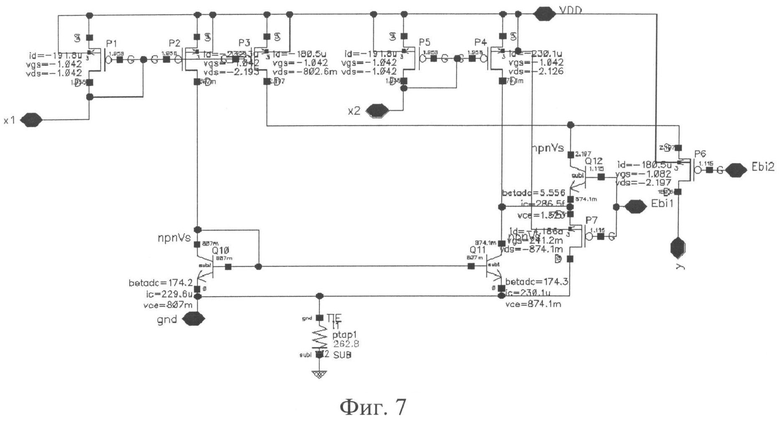

На фиг.7 показана схема логического элемента «2И» в среде компьютерного моделирования Cadence на моделях SiGe транзисторов.

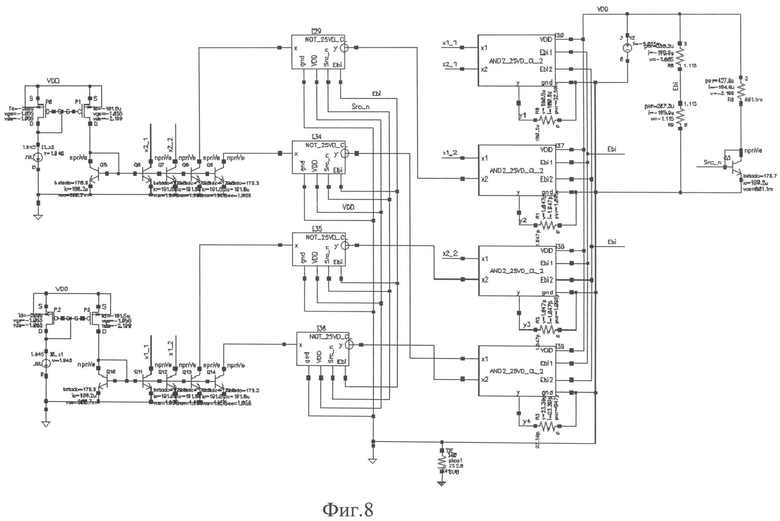

На фиг.8 представлена схема устройства фиг.2, включающая схему первого 20 и второго 28 размножителей сигналов, логические элементы «НЕ» и логические элементы «2И» в среде компьютерного моделирования Cadence на моделях SiGe транзисторов.

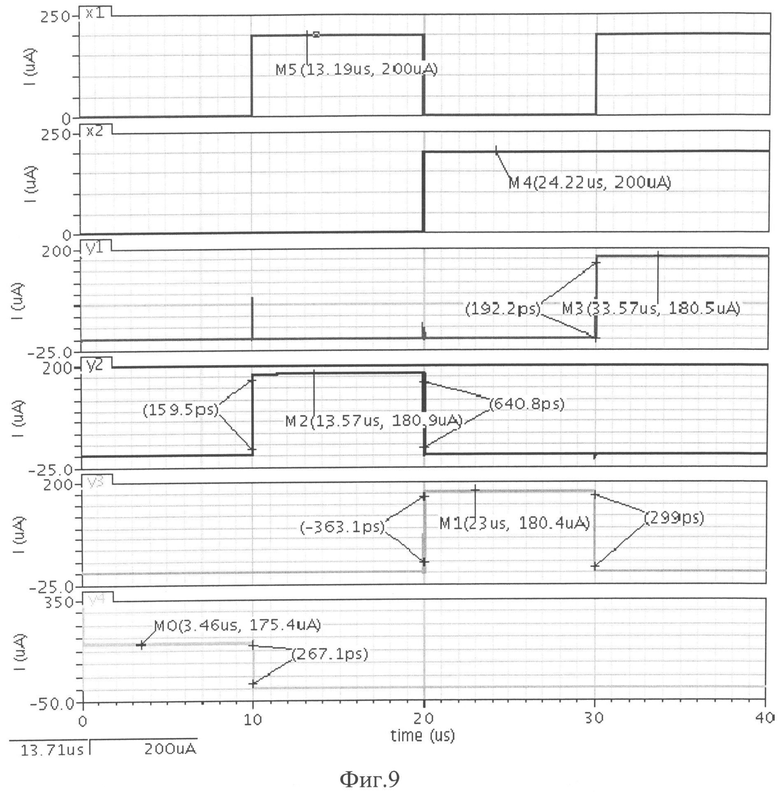

На фиг.9 показана осциллограмма входных и выходных токов устройства, соответствующих таблице истинности устройства.

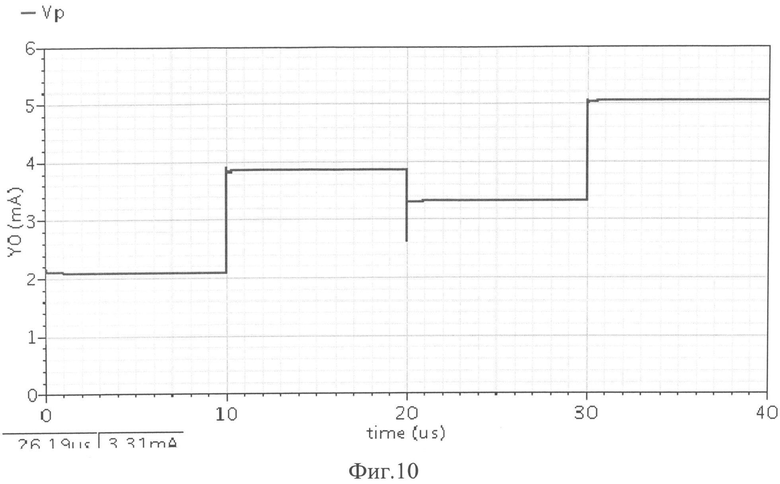

На фиг.10 приведена временная характеристика потребляемого тока устройства фиг.2 при Eп=3 В.

В логическое устройство «Дешифратор 2 в 4» по фиг.2, содержащее первый (1) и второй (2) входы устройства, первый (3), второй (4), третий (5) и четвертый (6) логические элементы «2И», выход первого (3) логического элемента «2И» соединен с первым (7) логическим выходом устройства, выход второго (4) логического элемента «2И» соединен со вторым (8) логическим выходом устройства, выход третьего (5) логического элемента «2И» соединен с третьим (9) логическим выходом устройства, выход четвертого (6) логического элемента «2И» соединен с четвертым (10) логическим выходом устройства, первый (11) логический элемент «НЕ», выход которого связан с первым (12) входом второго (4) логического элемента «2И», второй (13) логический элемент «НЕ», выход которого соединен с первым (14) входом четвертого (6) логического элемента «2И», введены первый (15) и второй (16) дополнительные логические элементы «НЕ», выход первого (15) дополнительного логического элемента «НЕ» соединен со вторым (17) входом четвертого (6) логического элемента «2И», выход второго (16) дополнительного логического элемента «НЕ» связан с первым (18) входом третьего (5) логического элемента «2И», причем первый (1) вход устройства связан со входом (19) первого (20) дополнительного размножителя сигнала, первый (21) выход первого (20) дополнительного размножителя сигнала соединен со вторым (22) входом третьего (5) логического элемента «2И», второй (23) выход первого (20) дополнительного размножителя сигнала соединен с первым (24) входом первого (3) логического элемента «2И», третий (25) выход первого (20) дополнительного размножителя сигнала соединен со входом первого (11) логического элемента «НЕ», четвертый (26) выход первого (20) дополнительного размножителя сигнала связан со входом первого (15) дополнительного логического элемента «НЕ», второй (2) вход устройства связан со входом (27) второго (28) дополнительного размножителя сигнала, первый (29) выход второго (28) дополнительного размножителя сигнала соединен со вторым (30) входом первого (3) логического элемента «2И», второй (31) выход второго (28) дополнительного размножителя сигнала соединен со вторым (32) входом второго (4) логического элемента «2И», третий (33) выход второго (28) дополнительного размножителя сигнала соединен со входом второго (16) дополнительного логического элемента «НЕ», четвертый (34) выход второго (28) дополнительного размножителя сигнала связан со входом второго (13) логического элемента «НЕ».

Кроме этого, на фиг.3, в соответствии с п.2 формулы изобретения первый (20) и второй (28) дополнительные размножители сигнала содержат вход (35), первый (36), второй (37), третий (38) и четвертый (39) выходы, первый (40) и второй (41) входные транзисторы, истоки которых соединены с первой (42) шиной источника питания, затворы объединены и подключены к стоку первого (40) входного транзистора и входу (35) каждого первого (20) и второго (28) дополнительных размножителей сигнала, сток второго (41) входного транзистора соединен с коллектором и базой первого (43) выходного транзистора, эмиттер которого соединен с эмиттерами второго (44), третьего (45), четвертого (46) и пятого (47) выходных транзисторов и связан со второй (48) шиной источника питания, база первого (43) входного транзистора соединена с базами второго (44), третьего (45), четвертого (46) и пятого (47) выходных транзисторов, причем коллектор второго (44) выходного транзистора связан с первым (36) выходом каждого первого (20) и второго (28) дополнительных размножителей сигналов, коллектор третьего (45) выходного транзистора связан со вторым (37) выходом каждого первого (20) и второго (28) дополнительных размножителей сигналов, коллектор четвертого (46) выходного транзистора связан с третьим (38) выходом каждого первого (20) и второго (28) дополнительных размножителей сигналов, коллектор пятого (47) выходного транзистора связан с четвертым (39) выходом каждого первого (20) и второго (28) дополнительных размножителей сигналов. Кроме этого, вход (35) соответствует входу (19) первого (20) дополнительного размножителя сигнала и входу (27) второго (28) дополнительного размножителя сигнала, первый (36) выход соответствует первому (21) выходу и первому (29) выходу вышеперечисленных размножителей сигналов, второй (37) выход соответствует второму (23) и второму (31) выходам вышеперечисленных размножителей сигналов, третий (38) выход соответствует третьему (25) и третьему (33) выходам вышеперечисленных размножителей сигналов, четвертый (39) выход соответствует четвертому (26) и четвертому (34) выходам вышеперечисленных размножителей сигналов.

На фиг.4, в соответствии с п.3 формулы изобретения, каждый первый (11) и второй (13) логические элементы «НЕ», а также первый (15) и второй (16) дополнительные логические элементы «НЕ» содержат первый (49) и второй (50) входные транзисторы, истоки которых соединены с первой (51) шиной источника питания, затворы объединены и подключены к стоку первого (49) входного транзистора и входу (52) каждого из вышеперечисленных логических элементов «НЕ» ((11), (13), (15), (16)), сток второго (50) входного транзистора соединен со второй (53) шиной источника питания через первый (54) опорный источник тока и подключен к эмиттеру первого (55) и истоку второго (56) выходных транзисторов, причем сток второго (56) выходного транзистора соединен со второй (53) шиной источника питания, коллектор первого (55) выходного транзистора является логическим выходом (57) каждого из вышеперечисленных логических элементов «НЕ» ((11), (13), (15), (16)), а база первого (55) и затвор второго (56) выходных транзисторов соединены с источником напряжения цепи согласования потенциалов (58). Кроме этого, первая (51) шина источника питания может соединяться с первой (42) шиной источника питания, а вторая (53) шина источника питания может соединяться со второй (48) шиной источника питания и иметь одинаковый потенциал, а вход (52) соответствует входам первого (11) и второго (13) логических элементов «НЕ», а также первого (15) и второго (16) дополнительных логических элементов «НЕ», а выход (57) соответствует выходам первого (11) и второго (13) логических элементов «НЕ», а также первого (15) и второго (16) дополнительных логических элементов «НЕ».

На фиг.5, в соответствии с п.4 формулы изобретения, каждый первый (3), второй (4), третий (5), четвертый (6) логические элементы «2И» содержат первый (59) и второй (60) логические входы, первый (61), второй (62), третий (63) транзисторы, затворы которых объединены и подключены к стоку первого (61) транзистора и первому (59) логическому входу каждого из вышеперечисленных логических элементов «2И», четвертый (64) и пятый (65) транзисторы, затворы которых объединены и подключены к стоку четвертого (64) транзистора и ко второму (60) логическому входу каждого из вышеперечисленных логических элементов «2И», истоки первого (61), второго (62), третьего (63), четвертого (64) и пятого (65) транзисторов соединены с первой (66) шиной источника питания, сток второго (62) транзистора соединен с коллектором и базой шестого (67) транзистора и подключен к базе седьмого (68) транзистора, коллектор седьмого (68) транзистора соединен со стоком пятого (65) транзистора, а также эмиттером восьмого (69) транзистора и истоком девятого (70) транзистора, сток третьего (63) транзистора соединен с коллектором восьмого (69) транзистора и истоком десятого (71) транзистора, база восьмого (69) транзистора, затвор девятого (70) транзистора и затвор десятого (71) транзистора подключены к источнику вспомогательного напряжения (72), сток десятого (71) выходного транзистора связан с выходом (73) каждого из вышеперечисленных логических элементов «2И», причем эмиттер шестого (67), седьмого (68) и сток девятого (70) транзисторов связаны со второй (74) шиной источника питания. Кроме этого, первая (66) шина источника питания может соединяться с первой (51) и первой (42) шинами источника питания, а вторая (74) шина источника питания может соединяться со второй (53) и второй (48) шинами источника питания и иметь одинаковый потенциал, а первый (59) логический вход соответствует первому (12) входу второго (4) логического элемента «2И», первому (14) входу четвертого (6) логического элемента «2И», первому (18) входу третьего (5) логического элемента «2И» и первому (24) входу первого (3) логического элемента «2И», второй (60) логический вход соответствует второму (17) входу четвертого (6) логического элемента «2И», второму (22) входу третьего (5) логического элемента «2И», второму (30) входу первого (3) логического элемента «2И» и второму (32) входу второго (4) логического элемента «2И», а выход (73) соответствует первому (7), второму (8), третьему (9) и четвертому (10) логическим выходам устройства.

Рассмотрим работу предлагаемой схемы дешифратора с токовыми входами и выходами фиг.2.

Синтез логической функции дешифратора 2 в 4 производится по известным функциям [11]:

где Xвх0.i,

Xвх1.i,

Реализация логической функции «НЕ» («инверсия») фиг.4 производится с помощью токового зеркала на транзисторах 49 и 50, источника опорного тока 54 и цепью согласования на транзисторах 55 и 56, причем коллектор транзистора 55 является выходом логического элемента «НЕ». Входной сигнал Bx.i в форме кванта тока подается на вход 52 токового зеркала на транзисторах 49 и 50, где вычитается из тока I0 источника опорного тока 54, равного току входного сигнала Bx.i со значением логической «1», и далее поступает на вход цепи согласования на транзисторах 55 и 56. Таким образом, если на входе элемента присутствует логическая «1», то на выходе устанавливается логический «0» или отсутствие тока.

Синтез логической функции «И» («конъюнкция») производится на основе представления ее в линейной алгебре. Это представление имеет следующий вид:

где x1, x2 - входные логические сигналы.

Как видно из приведенного описания, реализация устройства «Дешифратор 2 в 4» производится реализацией стандартных логических функций по линейной алгебре формированием разности квантов тока I0. Реализация элементов на токовых зеркалах позволяет во многих случаях снизить напряжение питания, а так как все элементы приведенной схемы работают в активном режиме, предполагающем отсутствие насыщения в процессе переключений, повышается общее быстродействие устройства. Использование стабильных значений квантов тока I0, а также определение выходного сигнала разностью этих токов обеспечивает малую зависимость функционирования схемы от внешних дестабилизирующих факторов (девиация питающего напряжения, радиационное и температурное воздействия, синфазная помеха и др.).

Показанные на чертежах фиг.9, фиг.10 результаты моделирования подтверждают указанные свойства заявляемых схем.

Таким образом, рассмотренные схемотехнические решения логического устройства «Дешифратор 2 в 4» характеризуются двоичным токовым представлением сигнала и могут быть положены в основу вычислительных и управляющих устройств, использующих линейную алгебру, частным случаем которой является булева алгебра.

Источники информации

1. Патент US 6243319 B1, fig.13.

2. Патент US 5604712 A.

3. Патент US 4514829 A.

4. Патент US 20120020179 A1.

5. Патент US 6920078 B2.

6. Патент US 6324117 B1, fig.3.

7. Патентная заявка US 20040018019 A1.

8. Патент US 5568061 A.

9. Патент US 5148480 A, fig.4.

10. Brzozowski I., Zachara L., Kos A. Universal design method of n-to-2n decoders // Mixed Design of Integrated Circuits and Systems (MIXDES), 2013 Proceedings of the 20th International Conference, 2013. - P.279-284, Fig.1.

11. Subramanyam M.V. Switching Theory and Logic Design / Firewall Media, 2011. Second, - 783 p., Fig.3.174.

12. SN74LVC1G139 2-to-4 Line Decoder [Электронный ресурс]. URL: http://www.ti.com/lit/ds/symlink/sn741vc1g139.pdf.

13. Chernov N.I., Yugai V.Y., Prokopenko N.N., et al. Basic Concept of Linear Synthesis of Multi-Valued Digital Structures in Linear Spaces // 11 th East-West Design & Test Symposium (EWDTS 2013). - Rostov-on-Don, 2013. - P.146-149.

14. Малюгин В.Д. Реализация булевых функций арифметическими полиномами // Автоматика и телемеханика, 1982. №4. С.84-93.

15. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

16. Чернов Н.И. Линейный синтез цифровых структур АСОИУ // Учебное пособие. - Таганрог: ТРТУ, 2004 г. - 118 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 32-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2023 |

|

RU2800768C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| Мультиплексор | 1990 |

|

SU1774491A1 |

| ВЫХОДНОЙ КАСКАД УСИЛИТЕЛЯ МОЩНОСТИ НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ТРАНЗИСТОРОВ | 2013 |

|

RU2523947C1 |

| Формирователь матричных команд | 2018 |

|

RU2707913C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ИСТОКОВЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ | 2013 |

|

RU2536671C1 |

| Устройство формирования импульсных сигналов и уровней постоянного напряжения на МДП транзисторах | 1986 |

|

SU1370752A1 |

| УСТРОЙСТВО СРАВНЕНИЯ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2236696C1 |

| Мультиплексор | 1990 |

|

SU1780185A1 |

Изобретение относится к области вычислительной техники, автоматики и может использоваться в различных цифровых структурах и системах автоматического управления, передачи информации. Техническим результатом является повышение быстродействия и создание устройства, в котором внутреннее преобразование информации производится в двузначной токовой форме сигналов, определяемое состоянием входных токовых двоичных сигналов. Устройство содержит четыре логических элемента НЕ, четыре логических элемента И, два размножителя сигналов. 3 з.п. ф-лы, 10 ил.

1. Логическое устройство «Дешифратор 2 в 4», содержащее первый (1) и второй (2) входы устройства, первый (3), второй (4), третий (5) и четвертый (6) логические элементы «2И», выход первого (3) логического элемента «2И» соединен с первым (7) логическим выходом устройства, выход второго (4) логического элемента «2И» соединен со вторым (8) логическим выходом устройства, выход третьего (5) логического элемента «2И» соединен с третьим (9) логическим выходом устройства, выход четвертого (6) логического элемента «2И» соединен с четвертым (10) логическим выходом устройства, первый (11) логический элемент «НЕ», выход которого связан с первым (12) входом второго (4) логического элемента «2И», второй (13) логический элемент «НЕ», выход которого соединен с первым (14) входом четвертого (6) логического элемента «2И», отличающийся тем, что в схему введены первый (15) и второй (16) дополнительные логические элементы «НЕ», выход первого (15) дополнительного логического элемента «НЕ» соединен со вторым (17) входом четвертого (6) логического элемента «2И», выход второго (16) дополнительного логического элемента «НЕ» связан с первым (18) входом третьего (5) логического элемента «2И», причем первый (1) вход устройства связан со входом (19) первого (20) дополнительного размножителя сигнала, первый (21) выход первого (20) дополнительного размножителя сигнала соединен со вторым (22) входом третьего (5) логического элемента «2И», второй (23) выход первого (20) дополнительного размножителя сигнала соединен с первым (24) входом первого (3) логического элемента «2И», третий (25) выход первого (20) дополнительного размножителя сигнала соединен со входом первого (11) логического элемента «НЕ», четвертый (26) выход первого (20) дополнительного размножителя сигнала связан со входом первого (15) дополнительного логического элемента «НЕ», второй (2) вход устройства связан со входом (27) второго (28) дополнительного размножителя сигнала, первый (29) выход второго (28) дополнительного размножителя сигнала соединен со вторым (30) входом первого (3) логического элемента «2И», второй (31) выход второго (28) дополнительного размножителя сигнала соединен со вторым (32) входом второго (4) логического элемента «2И», третий (33) выход второго (28) дополнительного размножителя сигнала соединен со входом второго (16) дополнительного логического элемента «НЕ», четвертый (34) выход второго (28) дополнительного размножителя сигнала связан со входом второго (13) логического элемента «НЕ».

2. Логическое устройство «Дешифратор 2 в 4» по п.1, отличающееся тем, что каждый первый (20) и второй (28) дополнительные размножители сигнала содержат вход (35), первый (36), второй (37), третий (38) и четвертый (39) выходы, первый (40) и второй (41) входные транзисторы, истоки которых соединены с первой (42) шиной источника питания, затворы объединены и подключены к стоку первого (40) входного транзистора и входу (35) каждого первого (20) и второго (28) дополнительных размножителей сигнала, сток второго (41) входного транзистора соединен с коллектором и базой первого (43) выходного транзистора, эмиттер которого соединен с эмиттерами второго (44), третьего (45), четвертого (46) и пятого (47) выходных транзисторов и связан со второй (48) шиной источника питания, база первого (43) входного транзистора соединена с базами второго (44), третьего (45), четвертого (46) и пятого (47) выходных транзисторов, причем коллектор второго (44) выходного транзистора связан с первым (36) выходом каждого первого (20) и второго (28) дополнительных размножителей сигналов, коллектор третьего (45) выходного транзистора связан со вторым (37) выходом каждого первого (20) и второго (28) дополнительных размножителей сигналов, коллектор четвертого (46) выходного транзистора связан с третьим (38) выходом каждого первого (20) и второго (28) дополнительных размножителей сигналов, коллектор пятого (47) выходного транзистора связан с четвертым (39) выходом каждого первого (20) и второго (28) дополнительных размножителей сигналов.

3. Логическое устройство «Дешифратор 2 в 4» по п.1, отличающееся тем, что каждый первый (11) и второй (13) логические элементы «НЕ», а также первый (15) и второй (16) дополнительные логические элементы «НЕ» содержат первый (49) и второй (50) входные транзисторы, истоки которых соединены с первой (51) шиной источника питания, затворы объединены и подключены к стоку первого (49) входного транзистора и входу (52) каждого из вышеперечисленных логических элементов «НЕ» ((11), (13), (15), (16)), сток второго (50) входного транзистора соединен со второй (53) шиной источника питания через первый (54) опорный источник тока и подключен к эмиттеру первого (55) и истоку второго (56) выходных транзисторов, причем сток второго (56) выходного транзистора соединен со второй (53) шиной источника питания, коллектор первого (55) выходного транзистора является логическим выходом (57) каждого из вышеперечисленных логических элементов «НЕ» ((11), (13), (15), (16)), а база первого (55) и затвор второго (56) выходных транзисторов соединены с источником напряжения цепи согласования потенциалов (58).

4. Логическое устройство «Дешифратор 2 в 4» по п.1, отличающееся тем, что каждый первый (3), второй (4), третий (5), четвертый (6) логические элементы «2И» содержат первый (59) и второй (60) логические входы, первый (61), второй (62), третий (63) транзисторы, затворы которых объединены и подключены к стоку первого (61) транзистора и первому (59) логическому входу каждого из вышеперечисленных логических элементов «2И», четвертый (64) и пятый (65) транзисторы, затворы которых объединены и подключены к стоку четвертого (64) транзистора и ко входу (60) каждого из вышеперечисленных логических элементов «2И», истоки первого (61), второго (62), третьего (63), четвертого (64) и пятого (65) транзисторов соединены с первой (66) шиной источника питания, сток второго (62) транзистора соединен с коллектором и базой шестого (67) транзистора и подключен к базе седьмого (68) транзистора, коллектор седьмого (68) транзистора соединен со стоком пятого (65) транзистора, а также эмиттером восьмого (69) транзистора и истоком девятого (70) транзистора, сток третьего (63) транзистора соединен с коллектором восьмого (69) транзистора и истоком десятого (71) транзистора, база восьмого (69) транзистора, затвор девятого (70) транзистора и затвор десятого (71) транзистора подключены к источнику вспомогательного напряжения (72), сток десятого (71) выходного транзистора связан с выходом (73) каждого из вышеперечисленных логических элементов «2И», причем эмиттер шестого (67), седьмого (68) и сток девятого (70) транзисторов связаны со второй (74) шиной источника питания.

| US 6243319 B1, 05.06.2001 | |||

| US 5148480 A, 15.09.1992 | |||

| US 2012020179 A1, 26.01.2012 | |||

| ДЕШИФРАТОР | 2005 |

|

RU2307405C2 |

| ЛИНЕЙНЫЙ ДЕШИФРАТОР | 1991 |

|

RU2032937C1 |

| Дешифратор адреса | 1989 |

|

SU1672526A1 |

| Параллельный дешифратор | 1981 |

|

SU1014030A1 |

Авторы

Даты

2015-04-10—Публикация

2014-04-02—Подача