00

00

00

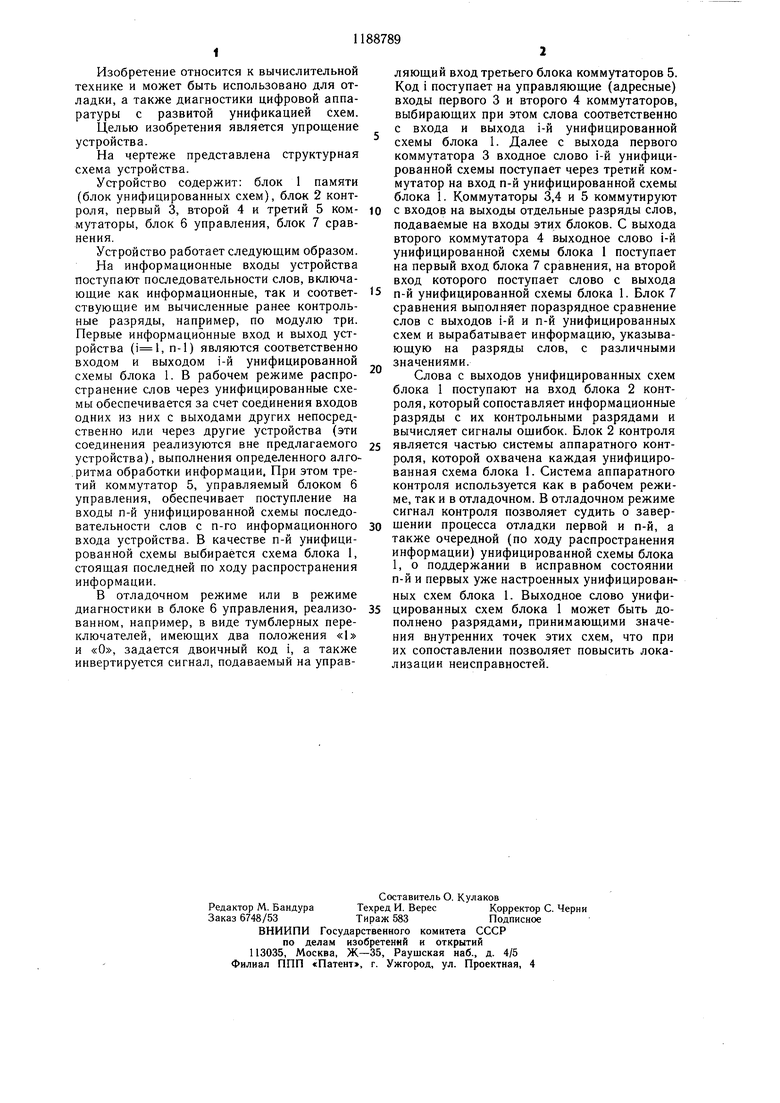

о Изобретение относится к вычислительной технике и может быть использовано для отладки, а также диагностики цифровой аппаратуры с развитой унификацией схем. Целью изобретения является упрощение устройства. На чертеже представлена структурная схема устройства. Устройство содержит: блок 1 памяти (блок унифицированных схем), блок 2 контроля, первый 3, второй 4 и третий 5 коммутаторы, блок 6 управления, блок 7 сравнения. Устройство работает следующим образом. На информационные входы устройства поступают последовательности слов, включающие как информационные, так и соответствующие им вычисленные ранее контрольные разряды, например, по модулю три. Первые информационные вход и выход устройства (, п-1) являются соответственно входом и выходом i-й унифицированной схемы блока 1. В рабочем режиме распространение слов через унифицированные схемы обеспечивается за счет соединения входов одних из них с выходами других непосредственно или через другие устройства (эти соединения реализуются вне предлагаемого устройства), выполнения определенного алгоритма обработки информации. При этом третий коммутатор 5, управляемый блоком 6 управления, обеспечивает поступление на входы п-й унифицированной схемы последовательности слов с п-го информационного входа устройства. В качестве п-й унифицированной схемы выбирается схема блока 1, стоящая последней по ходу распространения информации. В отладочном режиме или в режиме диагностики в блоке 6 управления, реализованном, например, в виде тумблерных переключателей, имеющих два положения «1 и «О, задается двоичный код i, а также инвертируется сигнал, подаваемый на управляющий вход третьего блока коммутаторов 5. Код i поступает на управляющие (адресные) входы первого 3 и второго 4 коммутаторов, выбирающих при этом слова соответственно с входа и выхода i-й унифицированной схемы блока 1. Далее с выхода первого коммутатора 3 входное слово i-й унифицированной схемы поступает через третий коммутатор на вход п-й унифицированной схемы блока 1. Коммутаторы 3,4 и 5 коммутируют с входов на выходы отдельные разряды слов, подаваемые на входы этих блоков. С выхода второго коммутатора 4 выходное слово i-й унифицированной схемы блока 1 поступает на первый вход блока 7 сравнения, на второй вход которого поступает слово с выхода п-й унифицированной схемы блока 1. Блок 7 сравнения выполняет поразрядное сравнение слов с выходов i-й и п-й унифицированных схем и вырабатывает информацию, указывающую на разряды слов, с различными значениями. Слова с выходов унифицированных схем блока 1 поступают на вход блока 2 контроля, который сопоставляет информационные разряды с их контрольными разрядами и вычисляет сигналы ощибок. Блок 2 контроля является частью системы аппаратного контроля, которой охвачена каждая унифицированная схема блока 1. Система аппаратного контроля используется как в рабочем режиме, так и в отладочном. В отладочном режиме сигнал контроля позволяет судить о заверщении процесса отладки первой и п-й, а также очередной (по ходу распространения информации) унифицированной схемы блока 1, о поддержании в исправном состоянии п-й и первых уже настроенных унифицированных схем блока 1. Выходное слово унифицированных схем блока 1 может быть дополнено разрядами, принимающими значения внутренних точек этих схем, что при их сопоставлении позволяет повысить локализации неисправностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для отладки программ | 1982 |

|

SU1100627A1 |

| Устройство для модификации адреса зон памяти при отладке программ | 1987 |

|

SU1465887A1 |

| Устройство для модификации адреса зон памяти при отладке программ | 1983 |

|

SU1161944A1 |

| ЦИФРОВОЙ ОТЛАДОЧНЫЙ КОМПЛЕКС | 2021 |

|

RU2773696C1 |

| Устройство для отладки программ | 1987 |

|

SU1425687A1 |

| Устройство для отладки микропроцессорных систем | 1986 |

|

SU1462326A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программ | 1989 |

|

SU1674135A1 |

| Устройство для отладки программ | 1980 |

|

SU960828A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее блок памяти, первый и второй коммутаторы, блок контроля, блок управления, блок сравнения, причем выход блока управления соединен с одними входами первого и второго коммутаторов, другие входы первого коммутатора подключены к входам группы блока памяти, выходы которого являются информационными выходами устройства, один выход блока памяти соединен с первым входом блока сравнения и одним входом блока контроля, другие входы которого подключены к другим выходам блока памяти, второй вход блока сравнения соединен с выходом второго коммутатора, другие входы которого подключены к другим выходам блока памяти, выходы блока контроля и блока сравнения являются контрольными выходами устройства, управляющим входом которого является вход блока управления, отличающееся тем, что, с целью упрощения устройства, в него введен третий коммутатор, первый вход которого подключен к выходу блока управления, выход первого коммутатора подключен к второму входу третьего коммутатора, выход i которого соединен с входом блока памяти, третий вход третьего коммутатора и входы (Л группы блока памяти являются информационными входами устройства.

| Устройство для поиска кратных неисправностей в однотипных логических блоках | 1978 |

|

SU781816A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1105944A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-10-30—Публикация

1984-03-27—Подача