Изобретение относится к вычислительной технике и может быть использовано для построения вычислительных систем, предназначенных для моделирования процессов, характеризующихся распределенными параметрами.

Цель изобретения - повышение производительности устройства за счет распараллеливания обработки информации.

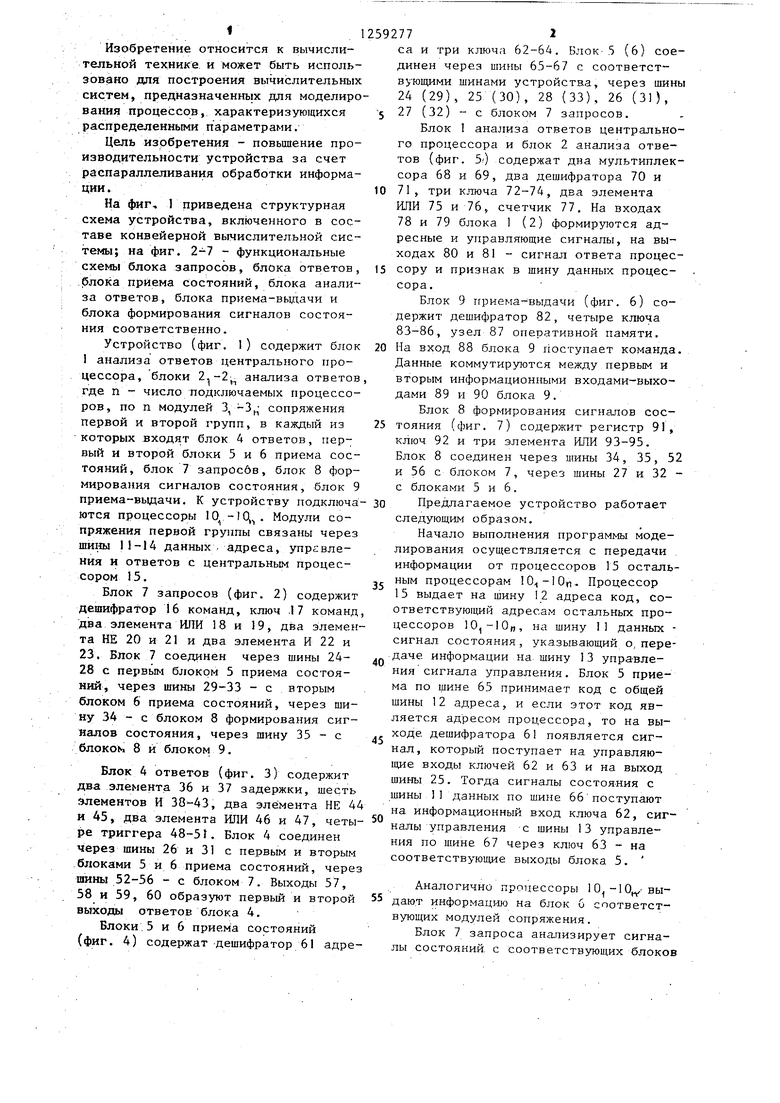

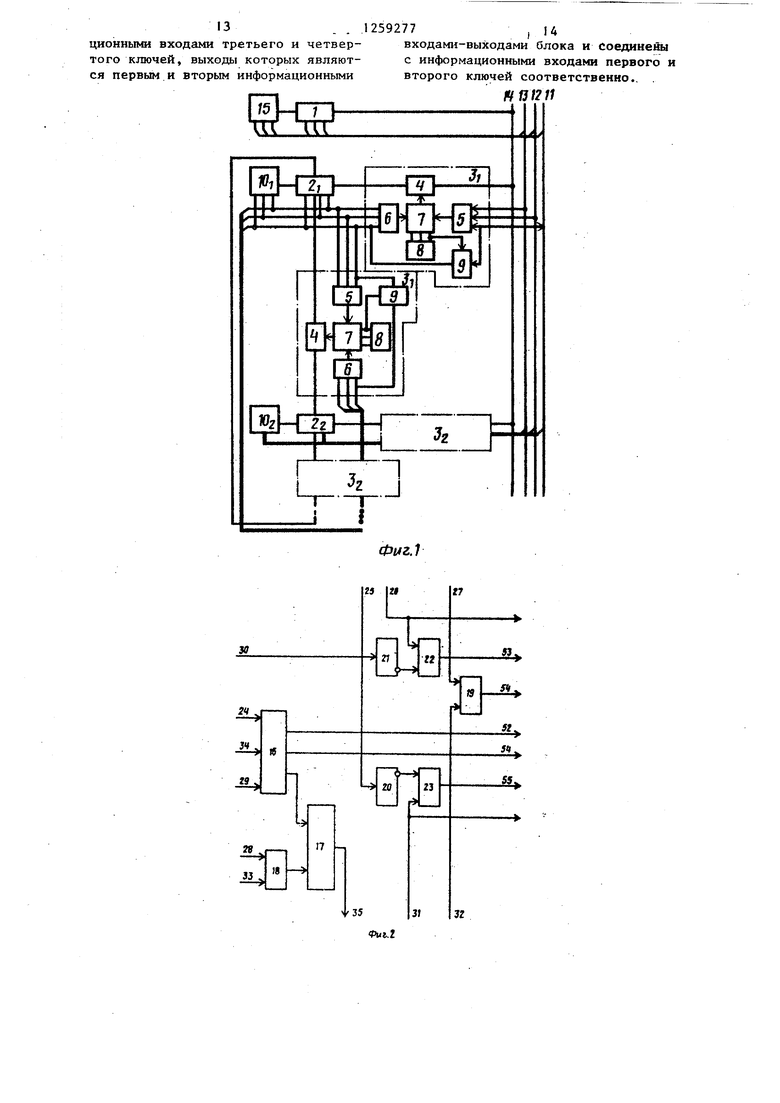

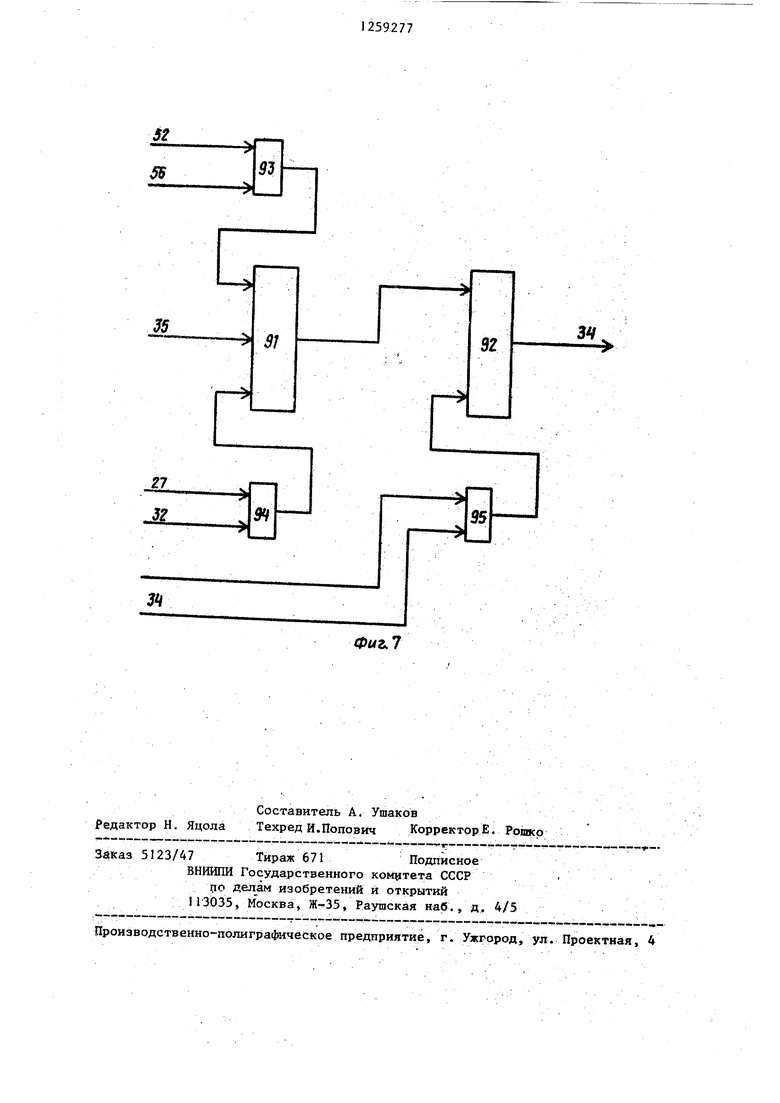

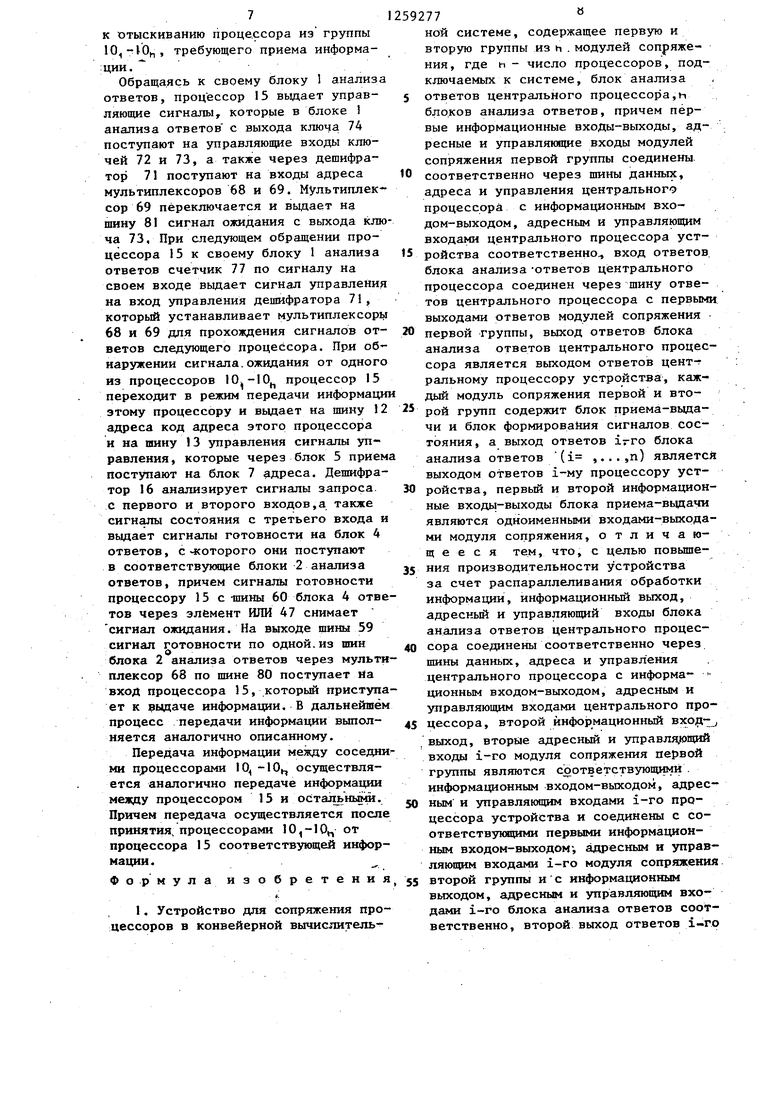

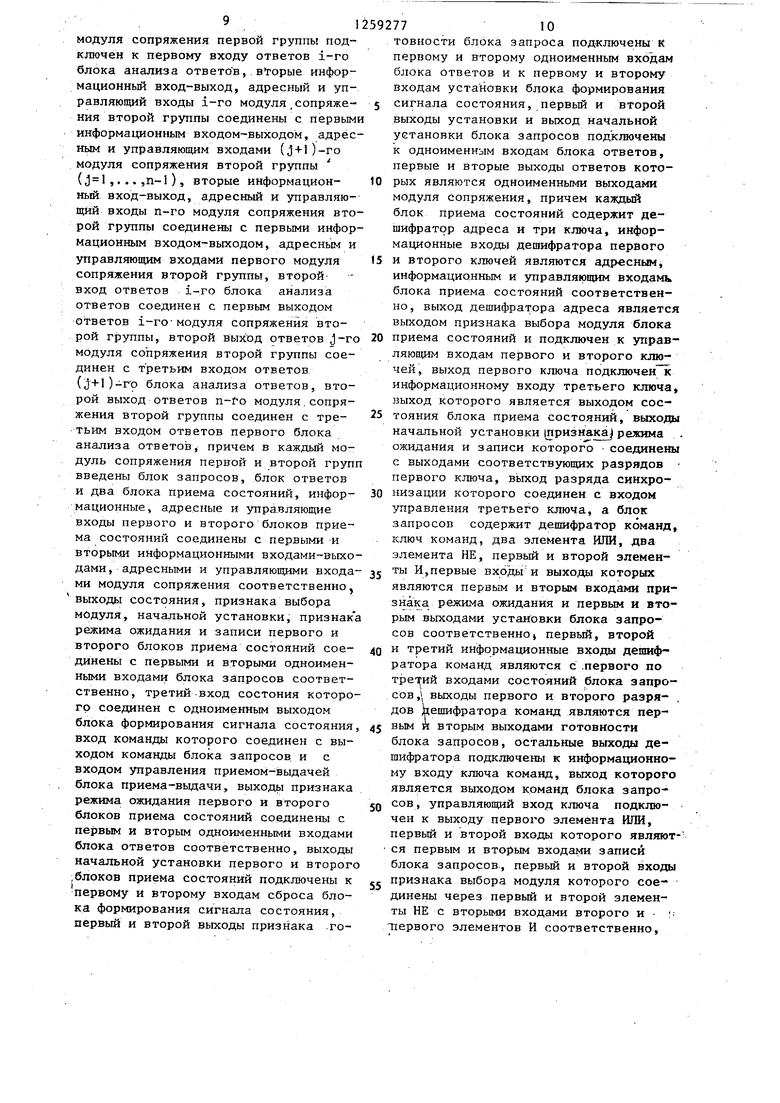

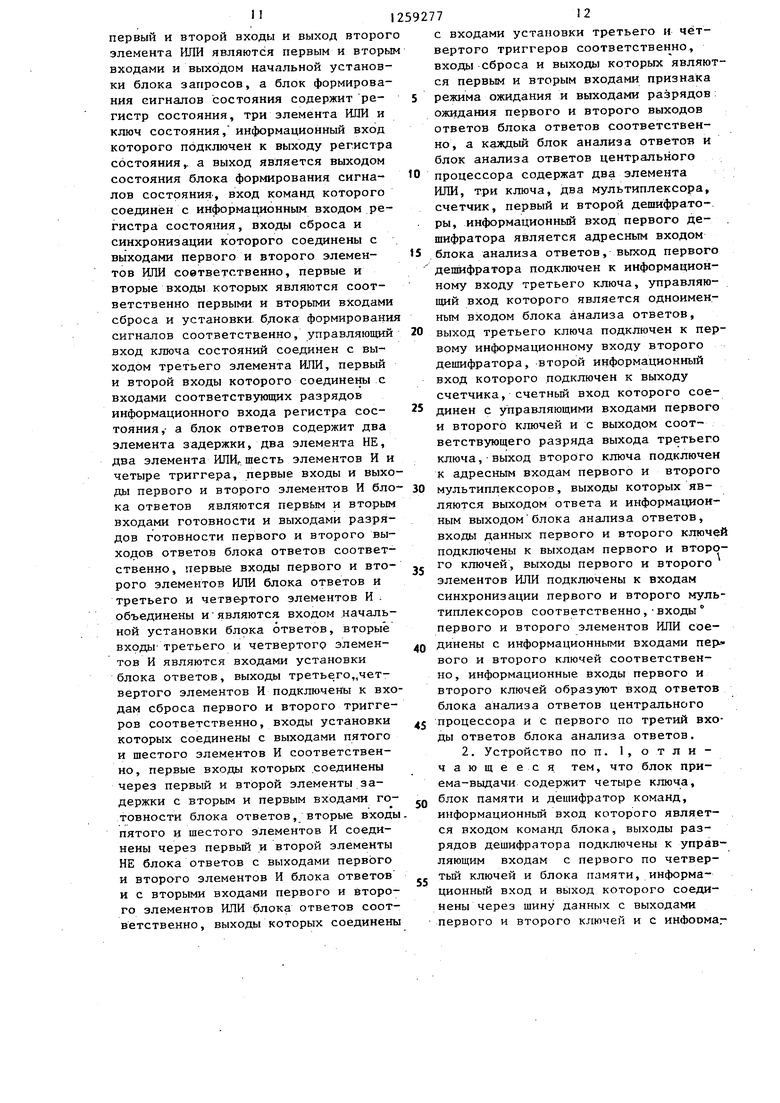

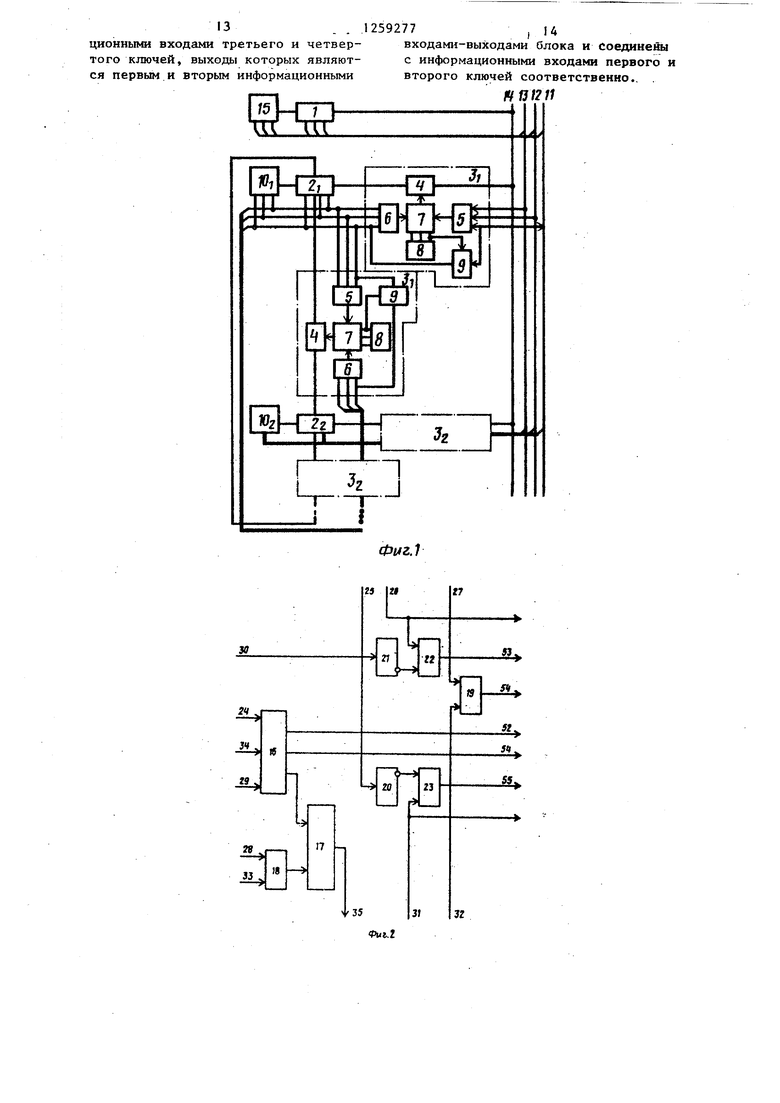

На; фиг, 1 приведена структурная схема устройства, включенного в составе конвейерной вычислительной системы; на фиг. 2-7 - функциональные

схемы блока запросов, блока ответов, блока приема состояний, блока анализа ответов, блока приема-вьщачи и блока формирования сигналов состояния соответственно.

Устройство (фиг, 1) содержит блок 1 анализа ответов центрального процессора, блоки анализа ответов где п - число подключаемых процессоров, по п модулей 3, сопряжения первой и второй групп, в каждый из которых входят блок 4 ответов, первый и второй блоки 5 и 6 приема состояний, блок 7 запросбв, блок 8 формирования сигналов состояния, блок 9 приема-выдачи. К устройству подключа ются процессоры ,. Модули сопряжения первой группы связаны через шиаы 11-14 данных , адреса, управления и ответов с центральным процессором 15.

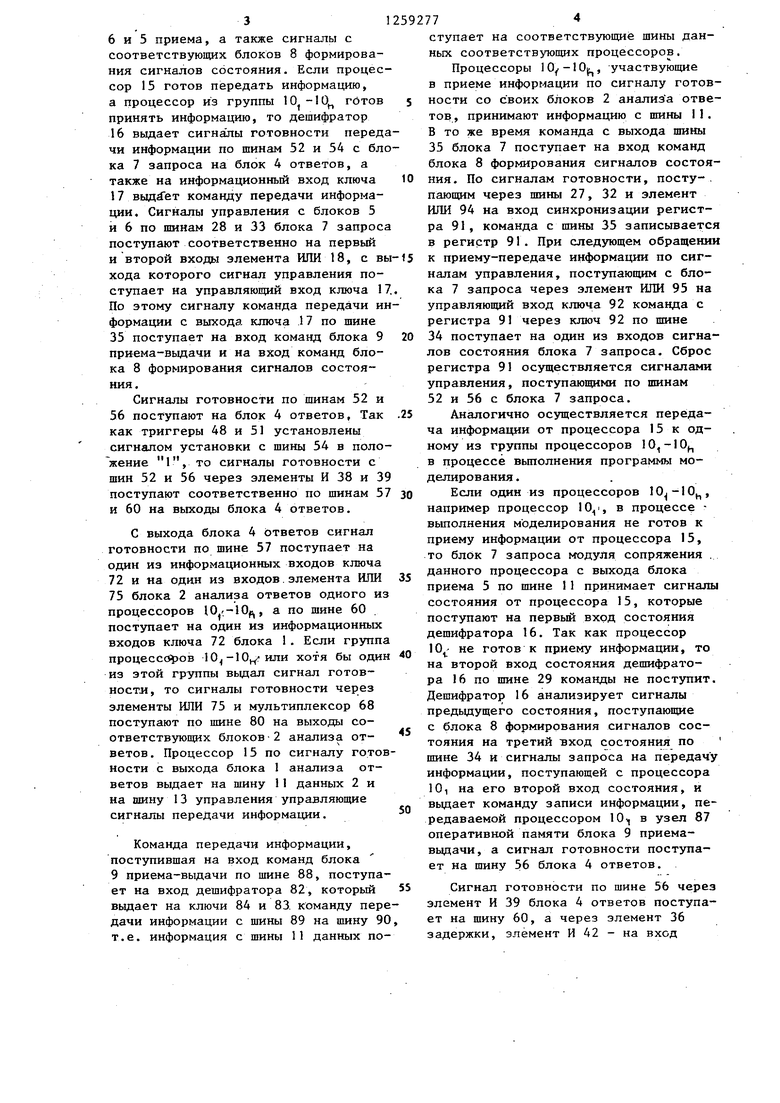

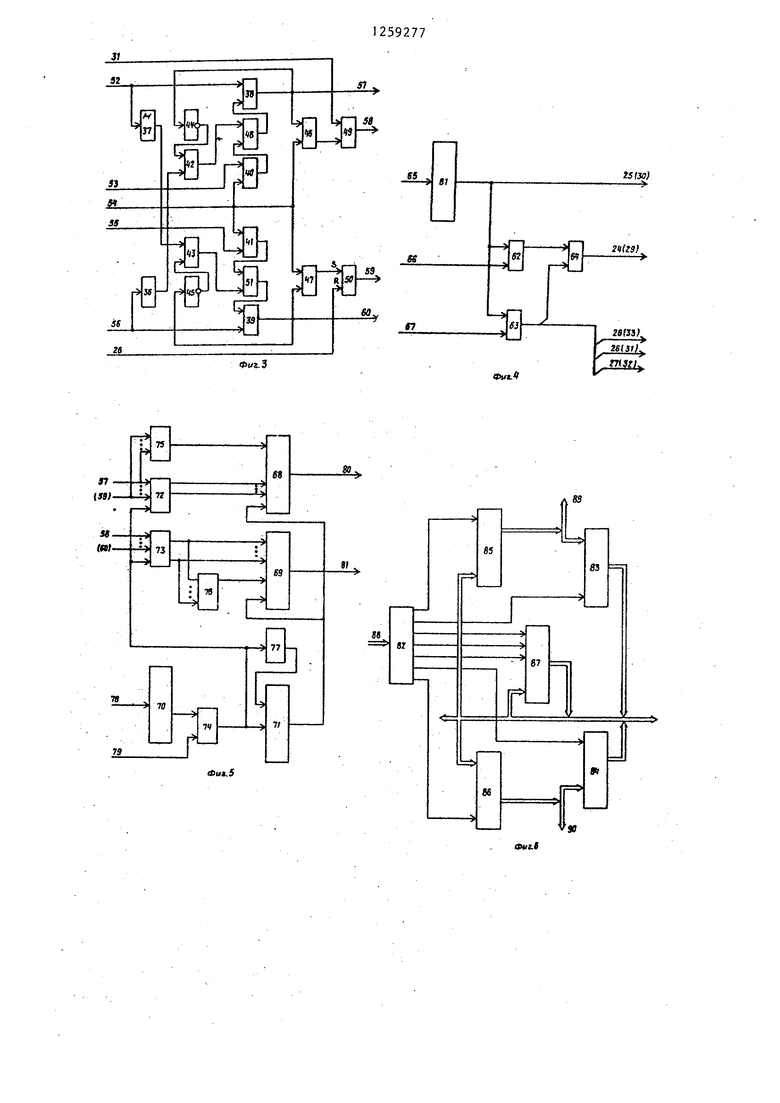

Блок 7 запросов (фиг. 2) содержит дешифратор 16 команд, ключ 17 команд два элемента ИЛИ 18 и 19, два элемента НЕ 20 и 21 и два элемента И 22 и 23. Блок 7 соединен через шины 24- 28 с первым блоком 5 приема состояний, через шины 29-33 - с вторым блоком 6 приема состояний, через шину 34 - с блоком 8 формирования сигналов состояния, через шину 35 - с блоком 8 и блоком 9.

Блок 4 ответов (фиг. 3) содержит два элемента 36 и 37 задержки, шесть элементов И 38-43, два элемента НЕ 44 и 45, два элемента ИЛИ 46 и 47, четы- ре триггера 48-5J. Блок 4 соединен через шины 26 и 31 с первым и вторым блоками 5 и 6 приема состояний, через шины 52-56 - с блоком 7. Выходы 57, 58 и 59, 60 образуют первый и второй выходы ответов блока 4.

Блоки.5 и 6 приема состояний (фиг. 4) содержат дешифратор 61 адре

5

5

О

0 5

са и три ключ; 62-64. Блок 5 (6) соединен через шины 65-67 с соответствующими шинами устройствл, через шины 24 (29), 25 (30), 28 (33), 26 (31), 27 (32) с блоком 7 запросов.

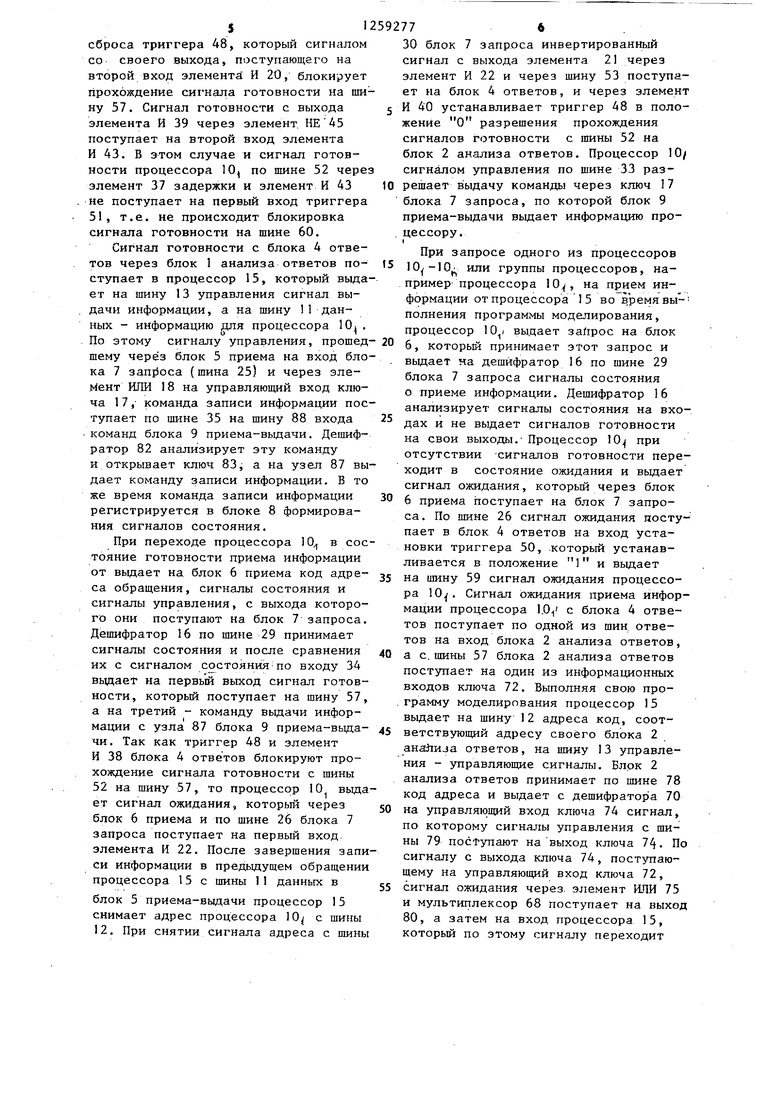

Блок 1 анализа ответов центрального процессора и блок 2 анализа ответов (фиг. 5;) содержат дна мультиплексора 68 и 69, два дешифратора 70 и 71, три ключа 72-74, два элемента ИЛИ 75 и 76, счетчик 77, На входах 78 и 79 блока 1 (2) формируются адресные и управляющие сигналы, на выходах 80 и 81 - сигнал ответа процессору и признак в шину данных процессора.

Блок 9 ггриема-выдачи (фиг. 6) содержит дешифратор 82, четыре ключа 83-86, узел 87 оперативной памяти. 0 На вход 88 блока 9 поступает команда. Данные коммутируются между первым и вторым информационными входами-выходами 89 и 90 блока 9.

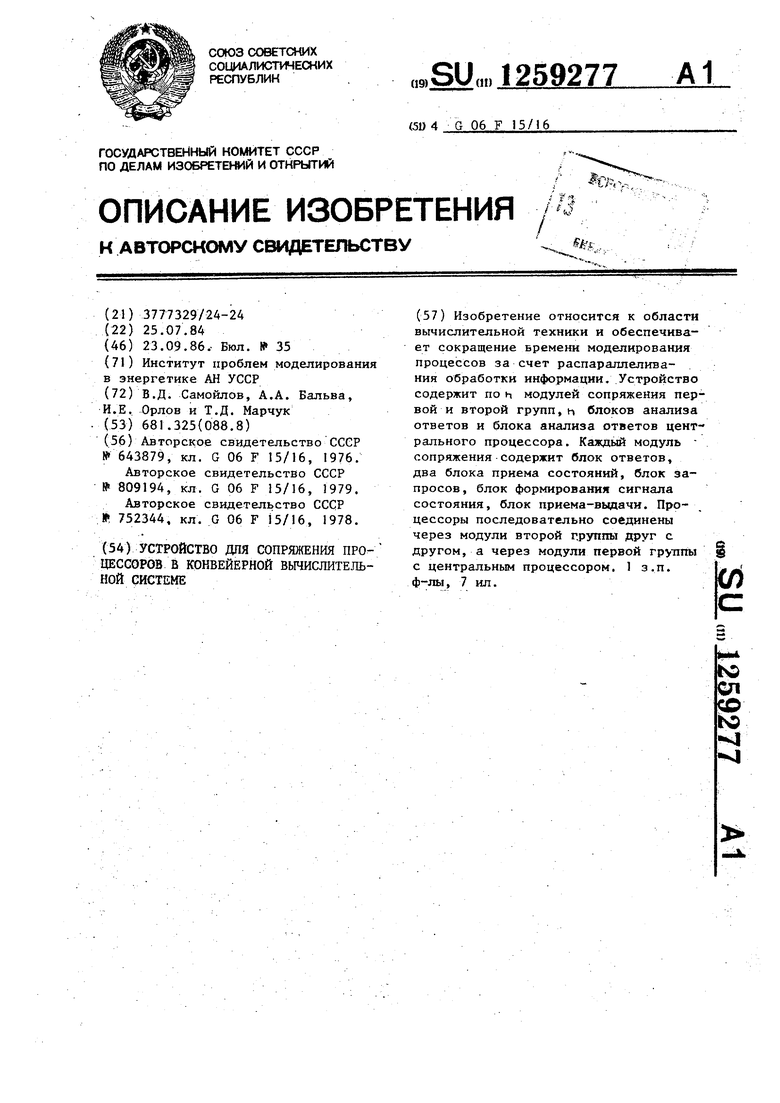

Блок 8 формирования сигналов состояния (фиг. 7) содержит регистр 91, ключ 92 и три элемента ИЛИ 93-95. Блок 8 соединен через шины 34, 35, 52 и 56 с блоком 7, через шины 27 и 32 - с блоками 5 и 6.

Предлагаемое устройство работает следующим образом.

Начало выполнения программы моделирования осуществляется с передачи информации от процессоров 15 остальным процессорам On- Процессор 15 выдает на шину 12 адреса код, соответствующий адресам остальных процессоров 10,-10, на шину II данных - сигнал состояния, указывающий о, передаче информации на шину I3 управления сигнала управления. Блок 5 приема по щине 65 принимает код с общей шины 12 адреса, и если этот код является адресом процессора, то на выходе дешифратора 61 появляется сигнал, который поступает на управляю- 1цие входы ключей 62 и 63 и на выход шины 25. Тогда сигналы состояния с шины 11 данных по шине 66 поступают на информационный вход ключа 62, сигналы управления с шины 13 управления по шине 67 через ключ 63 - на соответствуюиц е выходы блока 5.

5

0

5

Аналогично проиессоры выдают информацию на блок 6 соответствующих модулей сопряжения.

Блок 7 запроса анапизирует сигналы состояний, с соответствующих блоков

6 и 5 приема, а также сигналы с соответствующих блоков 8 формирования сигналов состояния, Если процессор 15 готов передать информацию, а процессор из группы готов принять информацию, то дешифратор

16вьщает сигналы готовности передачи информации по шинам 52 и 54 с блока 7 запроса на блок 4 ответов, а также на информационный вход ключа

17выдгГет команду передачи информации. Сигналы управления с блоков 5

и 6 по шинам 28 и 33 блока 7 запроса поступают соответственно на первый и второй входы элемента ИЛИ 18, с вы хода которого сигнал управления поступает на управляющий вход ключа 17 По этому сигналу команда передачи информации с выхода ключа 17 по шине 35 поступает на вход команд блока 9 приема-выдачи и на вход команд блока 8 формирования сигналов состояния .

Сигналы готовности по шинам 52 и 56 поступают на блок 4 ответов, Так как триггеры 48 и 51 установлены сигналом установки с шины 54 в поло- жение 1, то сигналы готовности с шин 52 и 56 через элементы И 38 и 39 поступают соответственно по шинам 57 и 60 на выходы блока 4 ответов,

С выхода блока 4 ответов сигнал готовности по шине 57 поступает на один из информационных входов ключа 72 и на один из входов.элемента ИЛИ 75 блока 2 анализа ответов одного из процессоров lOv-lOf, а по шине 60 поступает на один из информационных входов ключа 72 блока 1. Если группа процессоров хотя бы один из этой группы выдал сигнал готовности, то сигналы готовности через элементы ИЛИ 75 и мультиплексор 68 поступают по шине 80 на выходы соответствующих блоков2 анализа от- ветов. Процессор 15 по сигналу готовности с выхода блока 1 анализа ответов выдает на шину 11 данных 2 и на шину 13 управления управляющие

сигналы передачи информации.

Команда передачи информации, поступившая на вход команд блока 9 приема-вьщачи по шине 88, поступает на вход дешифратора 82, который 5S выдает на ключи 84 и 83. команду передачи информации с шины 89 на шину 90, т.е. информация с шины П данных поs

Ю

15 20

25 ЗО

5 0

0

S

ступает на соответствующие шины данных соответствующих процессоров.

Процессоры 10 -10|ц, участвую1цие в приеме информации по сигналу готовности со своих блоков 2 анализ а ответов , принимают информацию с шины 11. В то же время команда с выхода шины 35 блока 7 поступает на вход команд блока 8 формирования сигналов состояния. По сигналам готовности, посту-, пающим через шины 27, 32 и элемент ИЛИ 94 на вход синхронизации регистра 91 , команда с шины 35 записывается в регистр 91. При следующем обращении к приему-передаче информации по сигналам управления, поступающим с блока 7 запроса через элемент ИЛИ 95 на управляющий вход ключа 92 команда с регистра 91 через ключ 92 по шине 34 поступает на один из входов сигналов состояния блока 7 запроса. Сброс регистра 91 осуществляется сигналами управления, поступающими по шинам 52 и 56 с блока 7 запроса.

Аналогично осуществляется передача информации от процессора 15 к одному из группы процессоров 10,-10 в процессе выполнения программы моделирования .

Если один из процессоров , например процессор Ю, в процессе - выполнения моделирования не готов к приему информации от процессора 15, то блок 7 запроса модуля сопряжения . данного процессора с выхода блока приема 5 по шине 11 принимает сигналы состояния от процессора 15, которые поступают на первый вход состояния дешифратора 16. Так как процессор не готов к приему информации, то на второй вход состояния дешифратора 16 по шине 29 команды не поступит. Дешифратор 16 анализирует сигналы предьщущего состояния, поступающие с блока 8 формирования сигналов состояния на третий вход состояния по шине 34 и сигналы запроса на передачу информации, поступающей с процессора 10, на его второй вход состояния, и выдает команду записи информации, передаваемой процессором Юц в узел 87 оперативной памяти блока 9 приема- выдачи, а сигнал готовности поступает на шину 56 блока 4 ответов.

Сигнал готовности по шине 56 через элемент И 39 блока 4 ответов поступает на шину 60, а через элемент 36 задержки, элемент И 42 - на вход

сброса триггера 48, который сигналом со своего выхода, поступающего на второй вход элемента И 20, блокирует прохождение сигнала готовности на шину 57. Сигнал готовности с выхода элемента И 39 через элемент. НЕ 45 поступает на второй вход элемента И 43. В этом случае и сигнал готовности процессора 10 по шине 52 чере элемент 37 задержки и элемент И 43 не поступает на первый вход триггера 5, т.е. не происходит блокировка сигнала готовности на шине 60.

Сигнал готовности с блока 4 ответов через блок 1 анализа ответов поступает в процессор 15, который вьща ет на шину 13 управления сигнал выдачи информации, а на шину 11 дан

ных - информацию для процессора 10 , По этому сигналу управления, прошед- тему через блок 5 приема на вход блока 7 зап15оса (шина 25) и через элемент ИЛИ 18 на управляющий вход ключа 17,- команда записи информации поступает по шине 35 на шину 88 входа команд блока 9 приема-выдачи. Дешифратор 82 анализирует эту команду и открывает ключ 83, а на узел 87 выдает команду записи информации. В то же время команда записи информации регистрируется в блоке 8 формирования сигналов состояния.

При переходе процессора 10 в состояние готовности приема информации от выдает на блок 6 приема код адреса обращения, сигналы состояния и сигналы управления, с выхода которого они поступают на блок 7 запроса. Дешифратор 16 по шине 29 принимает сигналы состояния и после сравнения их с сигналом состояния по входу 34 выдает на первый выход сигнал готовности, который поступает на шину 57, а на третий - команду вьщачи информации с узла 87 блока 9 приема-вьща- чи. Так как триггер 48 и элемент И 38 блока 4 ответов блокируют прохождение сигнала готовности с шины 52 на шину 57, то процессор 10 вьща ет сигнал ожидания, который через блок 6 приема и по шине 26 блока 7 запроса поступает на первый вход элемента И 22. После завершения записи информации в предьодущем обращении процессора 15 с шины 1I даннык в

блок 5 приема-выдачи процессор 15 снимает адрес процессора 10 с шины 12. При снятии сигнала адреса с шины

20 25 ЗО

30 блок 7 запроса инвертированный сигнал с выхода элемента 21 через элемент И 22 и через шину 53 поступает на блок 4 ответов, и через элемент 5 И 40 устанавливает триггер 48 в положение О разрешения прохождения сигналов Готовности с тины 52 на блок 2 анализа ответов. Процессор 10/ сигналом управления по шине 33 разрешает выдачу команды через ключ 17 блока 7 запроса, по которой блок 9 приема-выдачи вьщает информацию процессору. I

При запросе одного из процессоров или группы процессоров, например процессора 10, на прием информации от процессора 15 во в.ремявыполнения программы моделирования,

10

15

5

0 5 О

0

0

5

5

процессор выдает зайрос на блок 6, который принимает этот запрос и вьщает на дешифратор 16 по шине 29 блока 7 запроса сигналы состояния о приеме информации. Дешифратор 16 анализирует сигналы состояния на входах и не выдает сигналов готовности на свои выходы. Процессор 10 при отсутствии -сигналов готовности переходит в состояние ожидания и выдает сигнал ожидания, которьш через блок 6 приема поступает на блок 7 запроса. По шине 26 сигнал ожидания поступает в блок 4 ответов на вход установки триггера 50, которьш устанавливается в положение 1 и выдает на шину 59 сигнал ожидания процессора 10.. Сигнал ожидания приема информации процессора 1. с блока 4 ответов поступает по одной из шиц ответов на вход блока 2 анализа ответов, а с. шины 57 блока 2 анализа ответов поступает на один из информационных входов ключа 72. Выполняя свою про- .грамму моделирования процессор 15 вьщает на шину 12 адреса код, соответствующий адресу своего блока 2 aнaJIИJa ответов, на шину 13 управления - управляющие сигналы. Блок 2 анализа ответов принимает по шине 78 код адреса и выдает с дешифратора 70 на управляющий вход ключа 74 сигнал, по которому сигналы управления с шины 79 посФупают на выход ключа 74. По сигналу с выхода ключа 74, поступающему на управляющий вход ключа 72, сигнал ожидания через, элемент ИЛИ 75 и мультиплексор 68 поступает на выход 80, а затем на вход процессора 15, который по этому сигналу переходит

7

к отыскиванию процессора из группы ,, требующего приема информации.

Обращаясь к своему блоку 1 анализа ответов, процессор 15 выдает управляющие сигналы, которые в блоке 1 анализа ответов с выхода ключа 74 поступают на управляющие входы ключей 72 и 73, а также через дешифратор 71 поступают на входы адреса мультиплексоров 68 и 69. Мультиплексор 69 переключается и выдает на шину 81 сигнал ожидания с выхода ключа 73, При следующем обращении процессора 15 к своему блоку 1 анализа ответов счетчик 77 по сигналу на своем входе выдает сигнал управления на вход управления дешифратора 71, который устанавливает мультиплексоры 68 и 69 для прохождения сигналов ответов следующего процессора. При обнаружении сигнала.ожидания от одного из процессоров 10.-10 процессор 15 переходит в режим передачи информаци этому процессору и выдает на шину 12 адреса код адреса этого процессора и на иииу 3 управления сигналы управления , которые через блок 5 прием поступают на блок 7 адреса. Дешифратор 16 анализирует сигналы запроса, с первого и второго входов,а также сигналы состояния с третьего входа и вьщает сигналы готовности на блок 4 ответов, с которого они поступают в соответствукяцие блоки 2 анализа ответов, причем сигналы готовности процессору 15 с тайны 60 блока 4 ответов через элемент ИЛИ 47 снимает сигнал ожидания. На выходе шины 59 сигнал готовности по одной.из шин блока 2 анализа ответов через мультиплексор 68 по шине 80 поступает На вход процессора 15, который приступает к выдаче информации. В дальнейшем процесс передачи информации выполняется аналогично описанному.

Передача информации между соседними процессорами 10 осуществляется аналогично передаче информации между процессором 15 и ос таль ньюет. Причем передача осуществляется после принятия, процессорами 10,-10,, от процессора 15 соответствующей информации.

Формула изобретения

.

1. Устройство для сопряжения процессоров в конвейерной вычислитель77«

ной системе, содержащее первую и вторую группы из h . модулей сопряжения, где h - число процессоров, подключаемых к системе, блок анализа ответов центрального процессора,и блоков анализа ответов, причем первые информационные входы-выходы, адресные и управляющие входы модулей сопряжения первой группы соединены

соответственно через шины данных, адреса и управления центрального процессора с информационным входом-выходом, адресным и управляющим входами центрального процессора устройства соответственно.., вход ответов блока анализа -ответов центрального процессора соединен через шину ответов центрального процессора с первыми выходами ответов модулей сопряжения

первой группы, выход ответов блока анализа ответов центрального процессора является выходом ответов цент- ральному процессору устройства, каждый модуль сопряжения первой и второй групп содержит блок приема-выдачи и блок формирования сигналов состояния , а выход ответов 1т-го блока анализа ответов (i ,...,п) является выходом ответов i-му процессору устройства, первый и второй информационные входь1-выходы блока приема-вьщачи являются одноименными входами-выходами модуля сопряжения, отличающееся тем, что, с целью повышения производительности устройства за счет распараллеливания обработки информации, информационный выход, адресный и управляющий входы блока анализа ответов центрального процессора соединены соответственно через. шины данных, адреса и управления центрального процессора с информа- ционным входом-выходом, адресным и управляющим входами центрального процессора, второй информационный вход-; выход, вторые адресный и управля ощий входы i-ro модуля сопряжения первой группы являются сЬответствующимй . информационным входом-выходом, адресным и управляющим входами i-ro процессора устройства и соединены с со- ответствуняцими первыми информационным входом-выходом; адресным и управ- ляннцим входами i-ro модуля сопряжения

второй группы и с информационным

выходом, адресным и управляющда входами i-ro блока анализа ответов соответственно, второй выход ответов i-го

модуля сопряжения первой группы подключен к первому входу ответов i-ro блока анализа ответо в,, в горые инфор- мационньй вход-выход, адресный и управляющий входы i-ro модуля , сопряжения второй группы соединены с первыми информационным входом-выходом, адресным и управляющим входами (j+1)-го модуля сопряжения второй группы (j l ,...,п-1), вторые информационный вход-выход, адресный и управляющий входы п-го модуля сопряжения второй группы соединены с первыми информационным входом-выходом, адресным и управляющим входами первого модуля сопряжения второй группы, второй вход ответов i-ro блока анализа ответов соединен с первым выходом ответов i-ro-модуля сопряжения второй группы, второй выход ответов J-ro модуля сопряжения второй группы соединен с третьим входом ответов (j+I )-г о блока анализа ответов, второй выход ответов п-Го модуля.сопряжения второй группы соединен с третьим входом ответов первого блока анализа ответов, причем в каждый модуль сопряжения первой и второй групп введены блок запросов, блок ответов и два блока приема состояний, информационные, адресные и управляющие входы первого и второго блоков приема состояний соединены с первыми и вторьпгш информационными входами-выходами, адресными и управляющими входа- 35 И,первые входы и выходы которых

ми модуля сопряжения соответственно, выходы состояния, признака выбора модуля, начальной установки, признак а режима ожидания и записи первого и второго блоков приема состояний сое- динены с первыми и вторыми одноимен- нь1ми входами блока запросов соответственно, третий вход состония которого соединен с одноименным выходом блока формирования сигнала состояния, вход команды которого соединен с выходом команды блока запросов, и с входом управления приемом-выдачей блока приема-выдачи, выходь признака режима ожидания первого и второго блоков приема состояний соединены с neisBbW и вторым одноименными входами блока ответов соответственно, выходы начальной установки первого и второго

блоков приема состояний подключены к первому и второму входам сброса блока формирования сигнала состояния, первый и второй выходы признака .готовности блока запроса подключены к первому и второму одноименным входам блока ответов и к первому и второму входам уста новки блока формирования

сигнала состояния, первый и второй выходы установки и выход начальной установки блока запросов подключены к одноименным входам блока ответов, первые и вторые выходы ответов которых являются одноименными выходами модуля сопряжения, причем каждый блок приема состояний содержит дешифратор адреса и три ключа, информационные входь дешифратора первого

и второго ключей являются адресным, информационным и управляющим входам. блока приема состояний соответственно, выход дешифратора адреса является выходом признака выбора модуля блока

приема состояний и подключен к управляющим входам первого и второго ключей, выход первого ключа подключен к информационному входу третьего ключа, выход которого является выходом сое-

тояния блока приема состояний, выходы начальной установки (признака режима ожидания и записи которого соединены с выходами соответствующих разрядов первого ключа, вьпсод разряда синхронизации которого соединен с входом управления третьего ключа, а блок запросов содержит дешифратор команд, ключ команд, два элемента ШШ, два элемента НЕ, первый и второй элемен

являются первым и вторым входами признака режима ожидания и первым и вторым выходами установки блока запросов соответственно первый, второй и третий информационные входы дешифратора команд являются с .первого по входами состояний блока запросов , выходы первого и второго разря- , дов дешифратора команд являются пер- вь1м и вторым выходами готовности блока запросов, остальные выходы дешифратора подключены к информационному входу ключа команд, выход которого является выходом команд блока запросов , управляющий вход ключа подклю- чей к выходу первого элемента ИЛИ, первый и второй входы которого являют- ся первым и вторым входами записи блока запросов, первый и второй входы признака выбора модуля которого соединены через первый и второй элементы НЕ с вторыми входами второго и г- TiepBoro элементов И соответственно.

первый и второй входы и выход второг элемента ИЛИ являются первым и вторы входами и выходом начальной установки блока запросов, а блок формирования сигналов состояния содержит регистр состояния, три элемента ИЛИ и ключ состояния, информационный вход которого подключен к выходу регистра состояния,, а выход является выходом состояния блока формирования сигналов СОСТОЯНИЯ , вход команд которого соединен с информационным входом регистра состояния, входы сброса и синхронизации которого соединены с выходами первого и второго элементов ИЛИ соетветственно, первые и вторые входы которых являются соответственно первыми и вторыми входами сброса и установки, б/юка формировани сигналов соответстаенно, управляющий вход ключа состояний соединен с выходом третьего элемента ИЛИ, первый и второй входы которого соединены с входами соответствующих разрядов информационного входа регистра состояния,- а блок ответов содержит два элемента задержки, два элемента НЕ, два элемента ИЛИ,-щесть элементов И и четыре триггера, первые входы и выходы первого и второго элементов И блока ответов являются первЬ м и вторым входами готовности и выходами разрядов готовности первого и второго выходов ответов блока ответов соответственно , первые входы первого и второго элементов ИЛИ блока ответов и третьего и четвертого элементов И; объединены иявляются входом начальной установки блока ответов, вторые входы-третьего и четвертого элементов И являются входами установки блока ответов, выходы третьего„чет- вертого элементов И подключены к входам сброса первого и второго триггеров соответственно, входы установки которых соединены с выходами пятого и шестого элементов И соответственно, первые входы которых соединены через первый и второй элементы задержки с вторым и первым входами готовности блока ответов, вторые входы пятого и шестого элементов И соединены через первый и второй элементы НЕ блока ответов с выходами первого и второго элементов И блока ответов и с вторыми входами первого и второго элементов ИЛИ блока ответов соответственно , выходы которых соединены

S

0

5

0

5

0

5

0

5

с входами установки третьего и четвертого триггеров соответственно, входы сброса и выходы которых являются первым и вторым входами признака режима ожидания и выходами разрядов ожидания первого и второго выходов ответов блока ответов соответственно, а каждый блок анализа ответов и блок анализа ответов центрального процессора содержат два элемента ИЛИ, три ключа, два мультиплексора, счетчик, первый и второй дешифрато-. ры, информационный вход первого де- . шифратора является адресным входом .блока анализа ответов, выход первого дешифратора подключен к информационному входу третьего ключа, управляющий вход которого является одноименным входом блока анализа ответов, выход третьего ключа подключен к первому информационному входу второго дешифратора, второй информационный вход которого подключен к выходу счетчика, счетный вход которого соединен с управляющими входами первого и второго ключей и с выходом соответствующего разряда выхода третьего ключа,-выход второго ключа подключен к адресным входам первого и второго мультиплексоров, выходы которых являются выходом ответа и информационным выходом блока анализа ответов, входы данных первого и второго ключей подключены к выходам первого и второго ключей, выходы первого и второго элементов ИЛИ подключены к входам синхронизации первого и второго мультиплексоров соответственно,-входы первого и второго элементов ИЛИ соединены с информационными входами первого и второго ключей соответственно, информационные входы первого и второго ключей образуют вход ответов блока анализа ответов центрального процессора и с первого по третий входы ответов блока анализа ответов.

2. Устройство по п. 1, о т л и - чающееся тем, что блок приема-выдачи содержит четыре ключа, блок памяти и дешифратор команд, информационный вход которого является входом команд блока, выходы разрядов дешифратора подключены к управляющим входам с первого по четвертый ключей и блока памяти, информационный вход и выход которого соединены через шину данных с выходами первого и второго ключей и с инфоомаг

13

ционными входами третьего и четвертого ключей, выходы которых являются первым и вторым информационными

1259277

14

входами-выходами блока и соединены с информационными входами первого и второго ключей соответственно.. .

ff13l211

Jgр- -

за

24 34

гз

W

17

35

Фиг.Г

19

п.

JL

Ч,

9-

га

а

5У,

31

зг

31

49

3J

SS

SI

tsix)

55

43

Vi

П «

Г

ss

2в

Ф(/г.З

66

№6Ч f-HJ

2V(Z3}

M

f}

evt

Фи&. 7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМИ ЯЧЕЙКАМИ РАСПРЕДЕЛИТЕЛЬНОЙ СЕТИ ШАХТЫ | 1990 |

|

RU2037205C1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для сопряжения процессоров в мультипроцессорной системе | 1984 |

|

SU1188747A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство для отладки управляющего комплекса сортировочной горки | 1984 |

|

SU1237528A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

Изобретение относится к области вычислительной техники и обеспечивает сокращение времени моделирования процессов за счет распараллеливания обработки информации. Устройство содержит по h модулей сопряжения первой и второй групп,h блоков анализа ответов и блока анализа ответов центрального процессора. Каждый модуль - сопряжения содержит блок ответов, два блока приема состояний, блок запросов , блок формирования сигнала состояния, блок приема-выдачи. Процессоры последовательно соединены через модули второй группы друг с другом, а через модули первой группы с центральным процессором, ф-лы, 7 ил. 1 з.п. (Л

| Микропроцессорное вычислительное устройство | 1976 |

|

SU643879A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительная система | 1979 |

|

SU809194A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мультипроцессорная вычислительная система | 1978 |

|

SU752344A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1984-07-25—Подача