Изобретение относится к вычислительной технике и- может быть использовано при настройке и отладке программного обеспечения микропроцессорных систем.

Целью изобретения является повышение быстродействия при отладке.

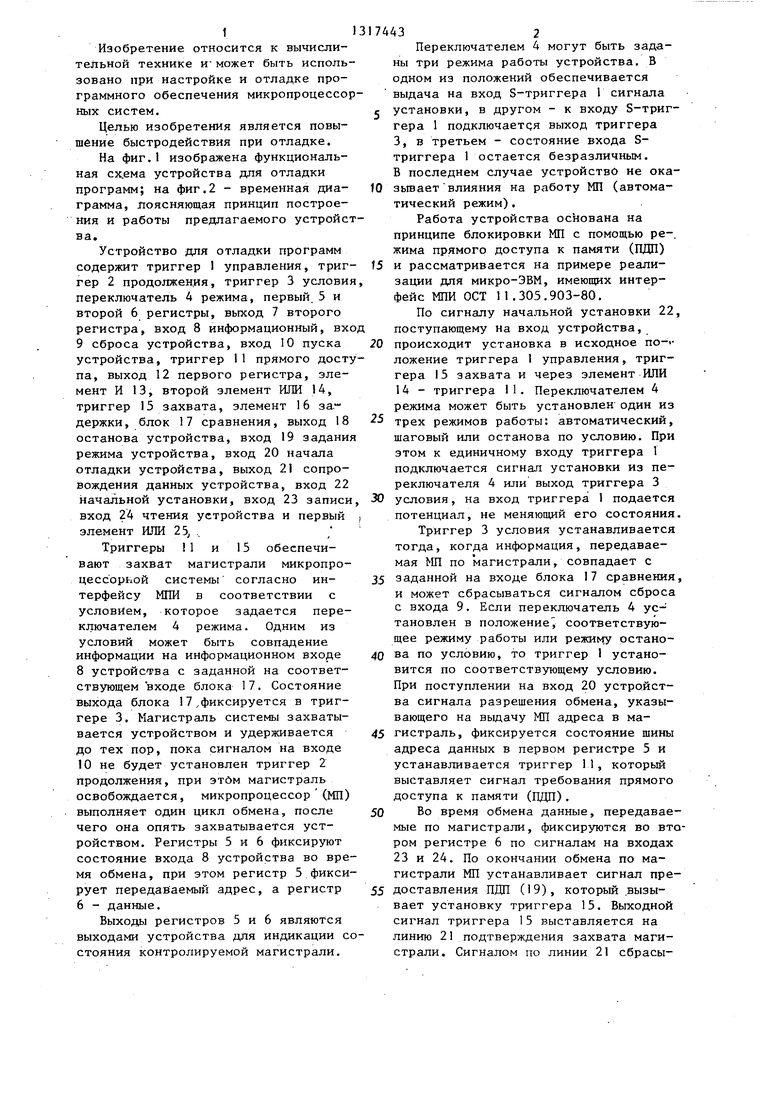

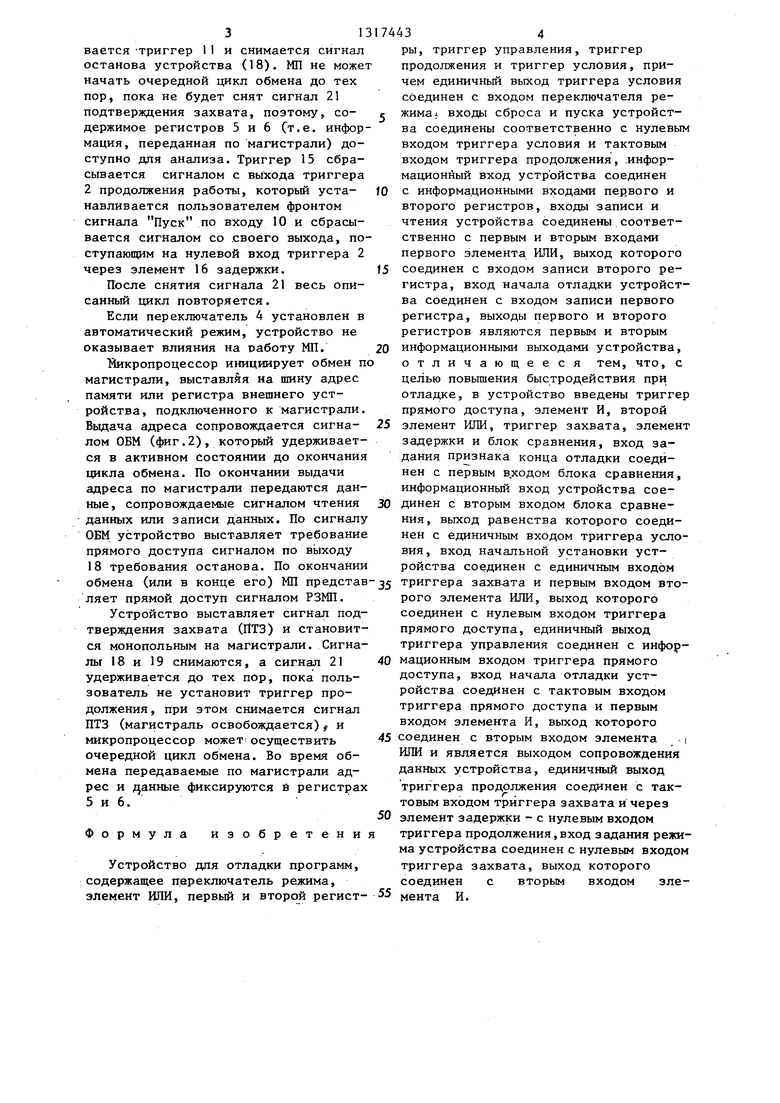

На фиг.1 изображена функциональная сх.ема устройства для отладки программ; на фиг.2 - временная диаграмма, Лоясняющая принцип построения и работы предлагаемого устройства.

Устройство для отладки программ содержит триггер 1 управления, триггер 2 продолжения, триггер 3 условия переключатель 4 режима, первый. 5 и второй 6 регистры, выход 7 второго регистра, вход 8 информационный, вхо

9сброса устройства, вход 10 пуска устройства, триггер 11 прямого доступа, выход 12 первого регистра, элемент И 13, второй элемент ИЛИ 14, триггер 15 захвата, элемент 16 за. держки, блок 17 сравнения, выход 18 останова устройства, вход 19 задания режима устройства, вход 20 начала отладки устройства, выход 21 сопровождения данных устройства, вход 22 начальной установки, вход 23 записи вход 24 чтения устройства и первый элемент ИЛИ 25, ..

Триггеры П и 15 обеспечивают захват магистрали микропроцессорной системы согласно интерфейсу МПИ в соответствии с условием, которое задается переключателем 4 режима. Одним из условий может быть совпадение информации на информационном входе 8 устройства с заданной на соответствующем входе блока 17. Состояние выхода блока 17 фиксируется в триггере 3. Магистраль системы захватывается устройством и удерживается до тех пор, пока сигналом на входе

10не будет установлен триггер 2 продолжения, при этим магистраль освобождается, микропроцессор (МП) выполняет один цикл обмена, после чего она опять захватывается устройством. Регистры 5 и 6 фиксируют состояние входа В устройства во время обмена, при этом регистр 5 фиксирует передаваемый адрес, а регистр

6 - данные.

Выходы регистров 5 и 6 являются выходами устройства для индикации состояния контролируемой магистрали.

0

5

5

0

Переключателем 4 могут быть заданы три режима работы устройства. В одном из положений обеспечивается выдача на вход S-триггера Г сигнала установки, в другом - к входу S-триггера 1 подключается выход триггера 3, в третьем - состояние входа S- триггера 1 остается безразличным. В последнем случае устройство не ока- зьгоает влияния на работу МП (автоматический режим),

Работа устройства основана на принципе блокировки МП с помощью ре-, жима прямого доступа к памяти (ПДП) и рассматривается на примере реализации для микро-ЭВМ, имеющих интерфейс МПИ ОСТ 11.305.903-80.

По сигналу начальной установки 22, поступающему на вход устройства, происходит установка в исходное по--- ложение триггера 1 управления, триггера 15 захвата и через элемент ИЛИ 14 - триггера 11. Переключателем 4 режима может быть установлен один из трех режимов работы: автоматический, шаговый или останова по условию. При этом к единичному входу триггера 1 подключается сигнал установки из переключателя 4 или выход триггера 3 условия, на вход триггера 1 подается потенциал, не меняющий его состояния.

Триггер 3 условия устанавливается тогда, когда информация, передаваемая МП по магистрали, совпадает с заданной на входе блока 17 сравнения, и может сбрасываться сигналом сброса с входа 9. Если переключатель 4 установлен в положение соответствующее режиму работы или режи останова по условию, то триггер 1 установится по соответствующему условию. При поступлении на вход 20 устройства сигнала разрешения обмена, указывающего на выдачу МП адреса в магистраль, фиксируется состояние шины адреса данных в первом регистре 5 и устанавливается триггер 11, который выставляет сигнал требования прямого доступа к памяти (ПДП).

Во время обмена данные, передаваемые по магистрали, фиксируются во втором регистре 6 по сигналам на входах 23 и 24. По окончании обмена по магистрали МП устанавливает сигнал пре- 5 доставления ПДП (19), который .вызывает установку триггера 15. Выходной сигнал триггера 15 выставляется на линию 21 подтверждения захвата магистрали. Сигналом по линии 21 сбрасы0

5

0

5

0

вается триггер 1 I и снимается сигнал останова устройства (18). МП не может начать очередной цикл обмена до тех пор, пока не будет снят сигнал 21 подтверждения захвата, поэтому, со- держимое регистров 5 и 6 Ст.е. информация, переданная по магистрали) доступно для анализа. Триггер 15 сбрасывается сигналом с выхода триггера 2 продолжения работы, который уста- навливается пользователем фронтом сигнала Пуск по входу 10 и сбрасывается сигналом со своего выхода, поступающим на нулевой вход триггера 2 через элемент 16 задержки.

После снятия сигнала 21 весь описанный цикл повторяется.

Если переключатель 4 установлен в автоматический режим, устройство не оказывает влияния на работу МП.

Микропроцессор инициирует обмен по магистрали, выставляя на шину адрес памяти или регистра внешнего устройства, подключенного к магистрали. Выдача адреса сопровождается сигна- лом ОБМ (фиг.2), который удерживается в активном состоянии до окончания цикла обмена. По окончании выдачи адреса по магистрали передаются данные, сопровождаемые сигналом чтения данных или записи данных. По сигналу ОБМ устройство выставляет требование прямого доступа сигналом по выходу 18 требования останова. По окончании

40

обмена (или в конце его) МП представ-35 триггера захвата и первым входом вто- ляет прямой доступ сигналом РЗМП.

Устройство выставляет сигнал подтверждения захвата (ПТЗ) и становится монопольным на магистрали. Сигналы 18 и 19 снимаются, а сигнал 21 удерживается до тех пор, пока пользователь не установит триггер продолжения , при этом снимается сигнал ПТЗ (магистраль освобождается)# и микропроцессор может осуществить очередной цикл обмена. Во время обмена передаваемые по магистрали адрес и ;aнныe фиксируются и регистрах 5 и 6.

Формула изобретения

рого элемента ИЛИ, выход которого соединен с нулевым входом триггера прямого доступа, единичный выход триггера управления соединен с информационным входом триггера прямого доступа, вход начала отладки устройства соединен с тактовым входом триггера прямого доступа и первым входом элемента И, выход которого 45 соединен с вторым входом элемента i ИЛИ и является выходом сопровождения данных устройства, единичный выход триггера продолжения соединен с тактовым входом триггера захвата и через элемент задержки - с нулевым входом триггера продолжения, в ход задания режима устройства соединен с нулевым входом триггера захвата, выход которого соединен с вторым входом элемента И.

50

Устройство дпя отладки программ, содержащее переключатель режима, элемент ИЛИ, первый и второй регист- 55

45

ры, триггер управления, триггер продолжения и триггер условия, причем единичный выход триггера условия соединен с входом переключателя режима j. входы сброса и пуска устройства соединены соответственно с нулевым входом триггера условия и тактовым входом триггера продолжения, .информационный вход устройства соединен с информационными входами первого и второго регистров, входы записи и чтения устройства соединены.соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с входом записи второго регистра, вход начала отладки устройства соединен с входом записи первого регистра, выходы первого и второго регистров являются первым и вторым информационными выходами устройства, отличающееся тем, что, с целью повьппения быстродействия при отладке, в устройство введены тригге прямого доступа, элемент И, второй элемент ИЛИ, триггер захвата, элемен задержки и блок сравнения, вход задания признака конца отладки соединен с первым в.ходом блока сравнения, информационный вход устройства соединен с вторым входом блока сравнения, выход равенства которого соединен с единичным входом триггера условия , вход начальной установки устройства соединен с единичным входом

40

35 триггера захвата и первым входом вто-

55

рого элемента ИЛИ, выход которого соединен с нулевым входом триггера прямого доступа, единичный выход триггера управления соединен с информационным входом триггера прямого доступа, вход начала отладки устройства соединен с тактовым входом триггера прямого доступа и первым входом элемента И, выход которого 45 соединен с вторым входом элемента ИЛИ и является выходом сопровождения данных устройства, единичный выход триггера продолжения соединен с тактовым входом триггера захвата и через элемент задержки - с нулевым входом триггера продолжения, в ход задания режима устройства соединен с нулевым входом триггера захвата, выход которого соединен с вторым входом элемента И.

50

Шина А11(в)

06М(20)

Редактор А.Маковская

Составитель И.Сигалов Техред В.Кадар

.Заказ 2425/44Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж - 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

, определяемое по/(ьзо8ателему t; Фиг.2

Корректор С.Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство для сопряжения | 1982 |

|

SU1051526A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

Изобретение относится к вычислительной технике и может быть использовано при настройке и отладке программного обеспечения микропроцессорных систем. Целью изобретения является повышение производительности при отладке. В состав устройства входят триггер 1 управления, триггер 2 продолжения, триггер 3 условия, переключатель 4 режима, первый 5, второй 6 регистры, триггер 11 ,;прямого доступа, элемент И 13, злемент ИЛИ 14, триггер 15 захвата, элемент 16 задержки, блок 17 сравнения. Сущность изобретения состоит в обеспечении возможности приостанавливать ход вычислительного процесса в требуемых точках, а также фиксировать в регистрах 5 и 6 состояние магистрали адреса и данных. 2 ил. п S. К(Л / со 4 4 00

| Устройство для отладки программ | 1983 |

|

SU1174932A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Bruce R | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1987-06-15—Публикация

1985-03-06—Подача