20

ь

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1298800A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970480A1 |

| Постоянное запоминающее устройство с коррекцией информации | 1988 |

|

SU1640741A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Постоянное запоминающее устройство с самоконтролем | 1984 |

|

SU1274005A1 |

| Устройство для сопряжения основной памяти с процессором | 1982 |

|

SU1037236A1 |

| Запоминающее устройство с исправлением ошибок | 1989 |

|

SU1667156A1 |

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1059629A2 |

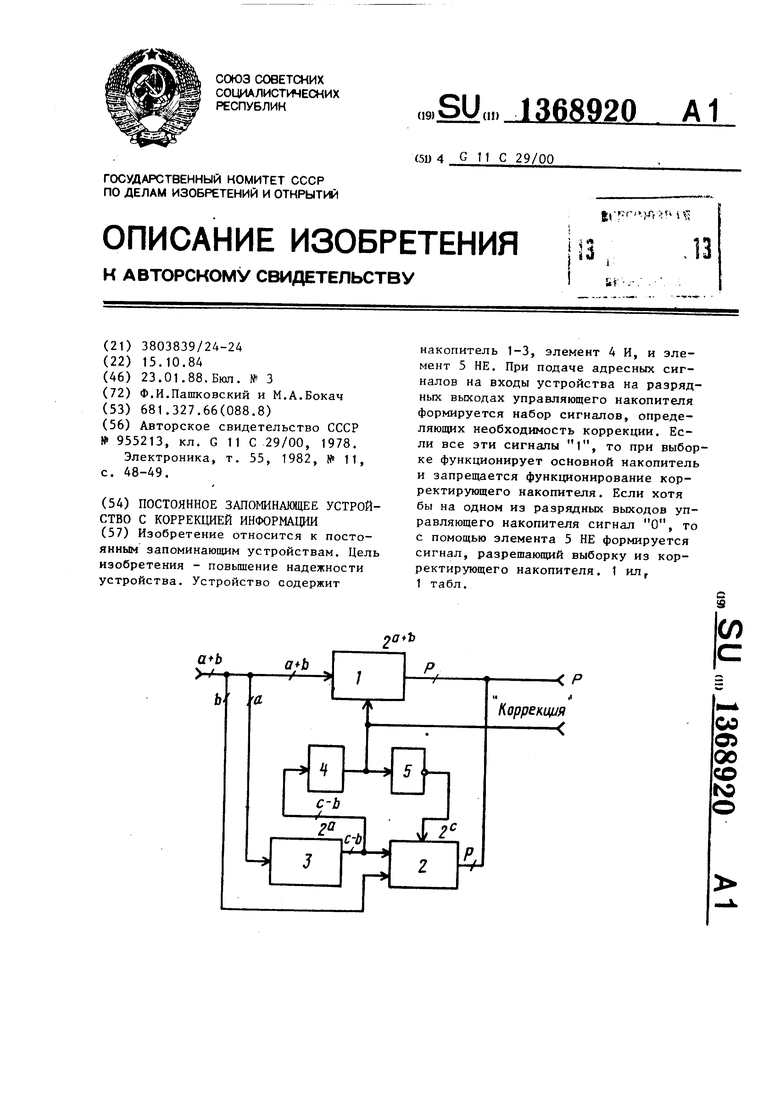

Изобретение относится к постоянным запоминающим устройствам. Цель изобретения - повышение надежности устройства. Устройство содержит накопитель 1-3, элемент 4 И, и элемент 5 НЕ. При подаче адресных сигналов на входы устройства на разрядных выходах управляющего накопителя формируется набор сигналов, определяющих необходимость коррекции. Если все эти сигналы 1, то при выбор ке функционирует основной накопитель и запрещается функционирование корректирующего накопителя. Если хотя бы на одном из разрядных выходов управляющего накопителя сигнал О, то с помощью элемента 5 НЕ формируется сигнал, разрешающий выборку из корректирующего накопителя. 1 ил, 1 табл. с 5

со а

СХ)

1C

Изобретение относится к постоянным запоминающим устройствам (ПЗУ).

Цель изобретения - повышение надежности устройства.

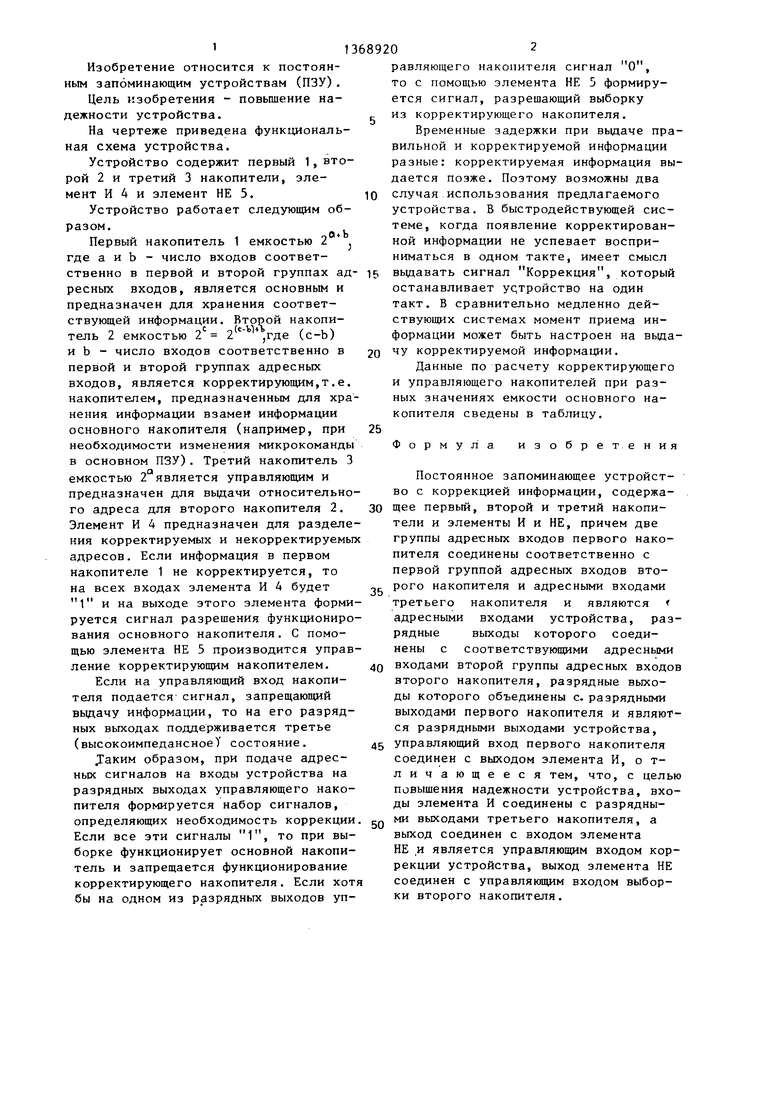

На чертеже приведена функциональная схема устройства.

Устройство содержит первый 1, второй 2 и третий 3 накопители, элемент И 4 и элемент НЕ 5.

Устройство работает следующим образом.

Первый накопитель 1 емкостью 2 где а и b - число входов соответственно в первой и второй группах ад ресных входов, является основным и предназначен для хранения соответствующей информации. Второй накопи„„с „(е-ЪТ+Ь / 1

тель 2 емкостью ,где (с-Ь) и b - число входов соответственно в первой и второй группах адресных входов, является корректирующим,т.е. накопителем, предназначенным для хранения информации взамен информации основного накопителя (например, при необходимости изменения микрокоманды в основном ПЗУ). Третий накопитель 3 емкостью 2°является управляюпшм и предназначен для вьщачи относительного адреса для второго накопителя 2. Элемент И 4 предназначен для разделения корректируемых и некорректируемы адресов. Если информация в первом накопителе 1 не корректируется, то на всех входах элемента И 4 будет 1 и на выходе этого элемента формируется сигнал разрешения функционирования основного накопителя, С помощью элемента НЕ 5 производится управление корректирующим накопителем.

Если на управляющий вход накопителя подается сигнал, запрещающий выдачу информации, то на его разрядных выходах поддерживается третье (высокоимпедансноеТ состояние.

Д аким образом, при подаче адресных сигналов на входы устройства на разрядных выходах управляющего накопителя формируется набор сигналов, определяющих необходимость коррекции Если все эти сигналы 1, то при выборке функционирует основной накопитель и запрещается функционирование корректирующего накопителя. Если хот бы на одном из разрядных выходов управляющего накопителя сигнал О, то с помощью элемента НЕ 5 формируется сигнал, разрешающий выборку из корректирующего накопителя.

Временные задержки при выдаче пра рильной и корректируемой информации разные: корректируемая информация выдается позже. Поэтому возможны два случая использования предлагаемого устройства. В быстродействующей системе, когда появление корректированной информации не успевает восприниматься в одном такте, имеет смысл вьщавать сигнал Коррекция, который останавливает уцтройство на один такт. В сравнительно медленно действующих системах момент приема информации может быть настроен на выдачу корректируемой информации.

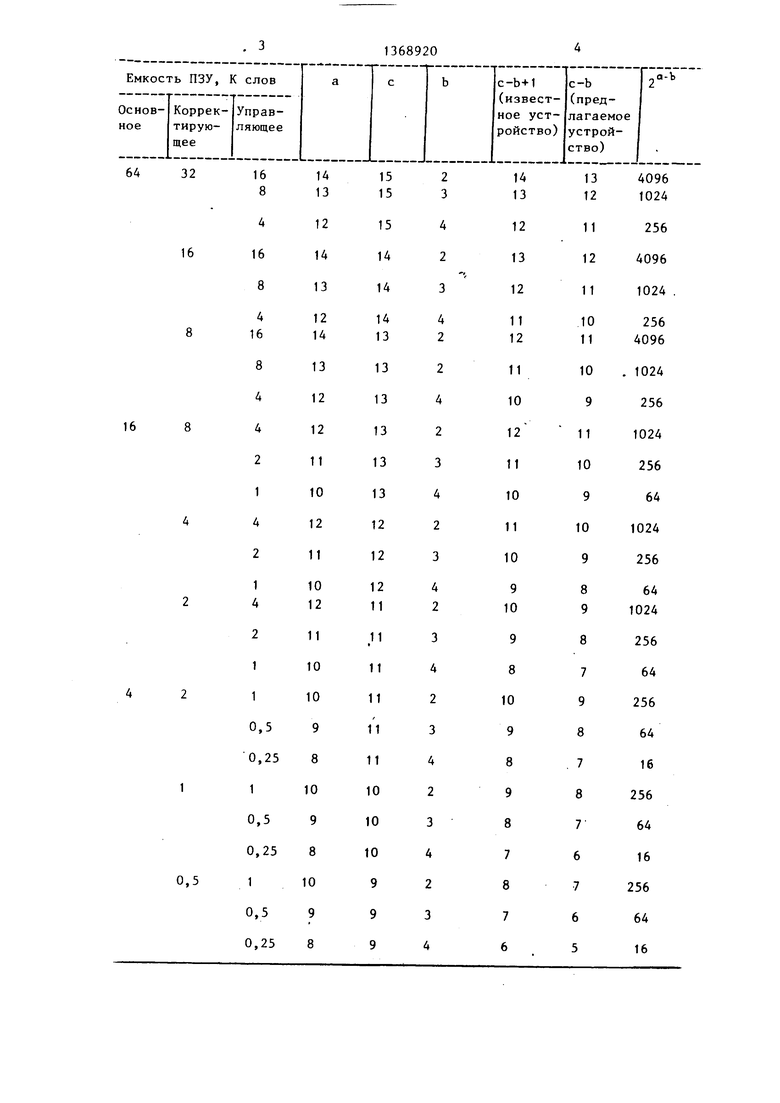

Данные по расчету корректирующего и управляющего накопителей при разных значениях емкости основного накопителя сведены в таблицу.

Формула изобретения

Постоянное запоминающее устройство с коррекцией информации, содержащее первый, второй и третий накопители и элементы И и НЕ, причем две группы адресных входов первого накопителя соединены соответственно с первой группой адресных входов второго накопителя и адресными входами третьего накопителя и являются адресными входами устройства, разрядные выходы которого соединены с Соответствующими адресными входами второй группы адресных входо второго накопителя, разрядные выходы которого объединены с. разрядными выходами первого накопителя и являются разрядными выходами устройства, управляющий вход первого накопителя соединен с выходом элемента И, о т- личающееся тем, что, с целью повышения надежности устройства, входы элемента И соединены с разрядными выходами третьего накопителя, а выход соединен с входом элемента НЕ и является управляющим входом коррекции устройства, выход элемента НЕ соединен с управляющим входом выборки второго накопителя.

| Способ создания породобетонной крепи | 1981 |

|

SU953213A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Электроника, т | |||

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

Авторы

Даты

1988-01-23—Публикация

1984-10-15—Подача