143

Изобретение относится к вычислительной технике и может быть применено для задержки передаваемой информации .

Цель изобретения - повьппение на-i дежности устройства.

На чертеже представлена структурная схема устройства.

Устройство содержит счетчик 1 адреса, первую группу коммутаторов 2, входной регистр 3, Накопитель 4, выходной регистр 5, вторую группу ком-. мутаторов 6, блок 7 формирования сигналов отказа, входы 8 код задержки, тактовый вход 9, информационные входы 10, информационные выходы 11. Коммутаторы 2 и 6 реализованы аналогичным образом.

Устройство работает следующим образом.

Рассмотрим его работу для случая задержки п-разрядного слова, состоящего из m 1-разрядных слогов, где т, .

В начальный момент времени на входы 8 счетчика 1 поступает код К за- держки и сопровождающие его сигналы приема, под действием которых счетчик 1 формирует и подает на адресньй вход накопителя 4 последовательность чений адреса, повторяемых через тактов работы устройства (каждое значение адреса - всего их К - устанавливается на время одного такта рабо- ты устройства).Такты работы устройства определяются синхроимпульсами типа меандр поступающими на вход 9. В первой половине такта происходит чтение информации из накопителя 4, на вход записи-чтения которого поступают синхроимпульсы, а по срезу синхроимпульса считанная информация записывается в выходной регистр 5, во второй половине такта информация из per гистра 3 записывается в ячейку нако-i пителя 4, из которой в первой половине такта считана информация.

На информационные входы коммутаторов 2 поступает слово, состоящее из m 1-разрядных слогов (каждый слоГ со своими контрольными разрядами).

Каждая из m групп коммутаторов 2 обрабатьшает соответствующий слог. На управляющие входы коммутаторов 2 поступают сигналы отказа, выработанные блоком 7 в результате обработки считанной информации в данном такте. Сигнал отказа равен логической 1, еезна -К

, л,

групп коммутато-

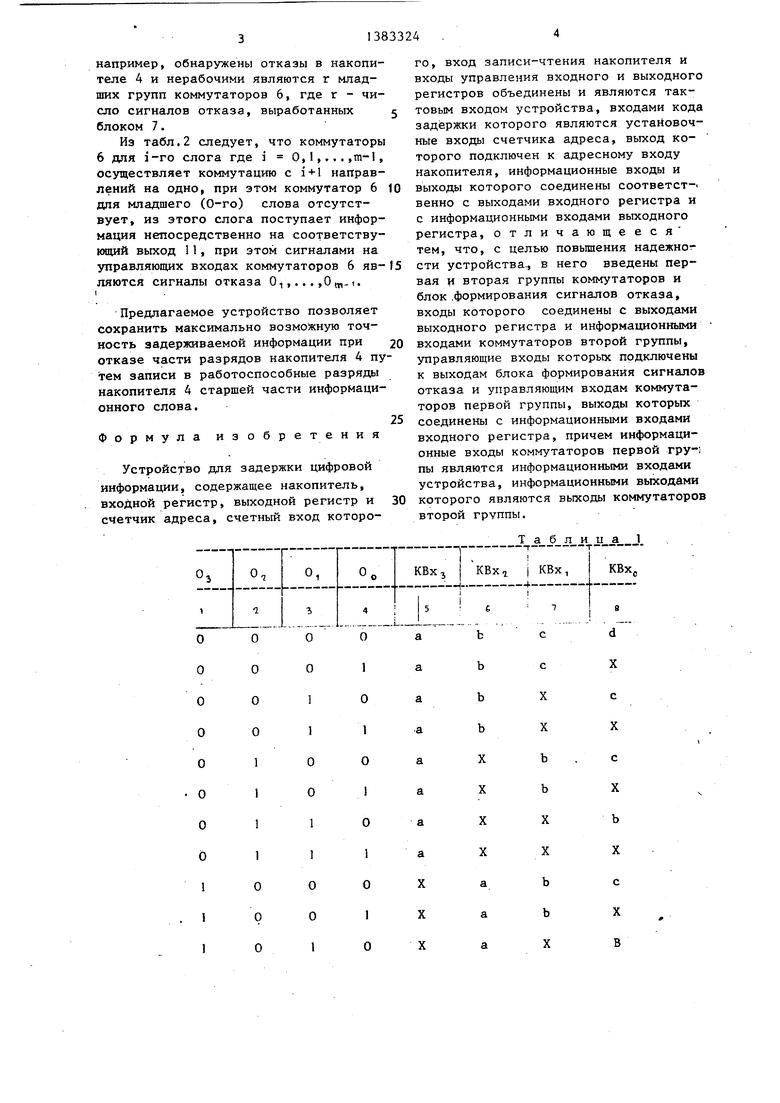

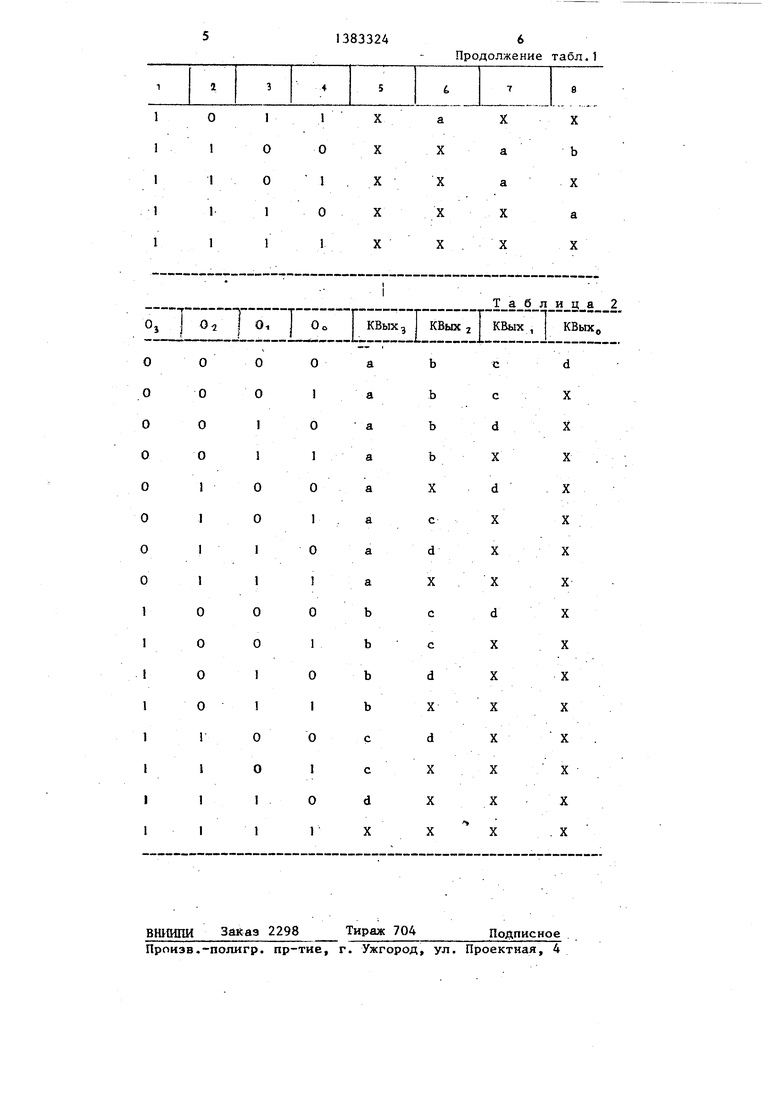

ли в слоге, которому он соответствует, произошел отказ. Сигнал отказа определяется в результате сравнения контрольных сигналов, сопровождающих каждый слог, с результатом вычисле-., ния контрольных разрядов в блоке 7 на основе считанной информации в данном такте. Рассмотрим работу коммутаторов 2 для случая слова, например, состоящего из четырех слогов а, в, с, d (где а-старший). Им соответствуют например, сигналы отказа О О,, 0, Од. Тогда работа коммутаторов 2 определяется табл. 1, где КВх., КВх, КВх, КВхд - выходы ров 2, при этом КВхэ - выходы, соответствующие старшей группе.

Знак X в табл.1 соответствует безразличному состоянию соответствующего из коммутаторов 2, поскольку по линии передачи информации, соответствующей этой группе коммутаторов, блок 7 выявил отказ.

Из табл.1 следует, что коммутатор 2 соответствующий i-му слогу, где О 4 i га,осуществляет коммутацию с m-i направлений на одно, причем ком-, мутатор 2 для i (m-l)-ro слова (например, для ) осуществляет связь соответствующего разряда регистра 3 с соответствующим из информационных входов 10. Управляющими сигналами коммутаторов 2 з-го слога являются

отказа О

1+1

О

, . .. ,0

Через регистр 3 информация поступает на накопитель 4, где задерживается на требуемое количество к так- тов. Из накопителя 4 задержанная информация поступает через регистр 5 в блок 7 к на входы коммутаторов 6.

Каждая из m групп коммутаторов 6 обрабатывает соответствующий слог информационного слова.

На управляющие входы коммутаторов 6 поступают m сигналов отказа из блока 7, Рассмотрим работу выходного коммутатора также для случая записи в накопитель 4 слова из четырех слогов а, Ь, с, d, (а - старший слог). Работа коммутаторов 6 описывается табл,2, где КВых 3, КВых, КВьпСо - сигналы на выходах коммутаторов 6 группы, соответствующей слогу, из которых К Вых 3 - выходы коммутаторов 6 группы, соответствующей старшему слогу.

Значение X в табл.2 соответствует безразличному состоянию соответствующего коммутатора 6 для случая, когда, .

например, обнаружены отказы в накопителе 4 и нерабочими являются г младших групп коммутаторов 6, где г - число сигналов отказа, выработанных блоком 7.

Из табл.2 следует, что коммутаторы 6 для i-ro слога где i 0,1,.. . ,tn-I, осуществляет коммутацию с i+l направлений на одно, при этом коммутатор 6 для младшего (0-го) слова отсутствует, из этого слога поступает информация нетюсредственно на соответствующий выход 11, при этом сигналами на управляющих входах коммутаторов 6 являются сигналы отказа Oi,...,.

Предлагаемое устройство позволяет сохранить максимально возможную точность задерживаемой информации при отказе части разрядов накопителя 4 путем записи в работоспособные разряды накопителя 4 старшей части информационного слова.

Формула изобретения

Устройство для задержки цифровой информации, содержащее накопитель, входной регистр, выходной регистр и счетчик адреса, счетный вход которого, вход записи-чтения накопителя и входы управления входного и выходного регистров объединены и являются тактовым входом устройства, входами кода задержки которого являются установочные входы счетчика адреса, выход которого подключен к адресному входу накопителя, информационные входы и выходы которого соединены соответст-i венно с выходами входного регистра и с информационными входами выходного регистра, отличающееся тем, что, с целью повышения надежно - сти устройства., в него введены первая и вторая группы коммутаторов и блок .формирования сигналов отказа, входы которого соединены с выходами выходного регистра и информационными входами коммутаторов второй группы, управляющие входы которых подключены к выходам блока формирования сигналов отказа и управляющим входам коммутаторов первой группы, выходы которых соединены с информационными входами входного регистра, причем информационные входы коммутаторов первой тру; пы являются информационными входами устройства, информационными выходами которого являются выходы коммутаторов второй группы.

т а б л и и а 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство для задержки цифровой информации | 1986 |

|

SU1383322A1 |

| Устройство для задержки цифровой информации с контролем | 1987 |

|

SU1462424A1 |

| Запоминающее устройство | 1978 |

|

SU926712A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Устройство для ввода и вывода динамически изменяющейся информации | 1982 |

|

SU1115043A1 |

Изобретение относится к вычислительной технике и может быть примене но для задержки передаваемой информации. Целью изобретения является повышение надежности устройства. Устройство содержит счетчик 1 адреса, первую группу коммутаторов 2, входной регистр 3, накопитель 4, выходной регистр 5, вторую группу коммутаторов 1 6, блок 7 формирования сигналов отказа, входы 8 кода задержки, тактовый вход 9, информационные входы 10 и информационные выходы 11. С -каждым так- т-лм из очередной ячейки накопителя . ; считывается информационное слово и в нее записывается новое информационное слово. Блок 7 осуществляет выборку контрольных сигналов из считанной из накопителя 4 информации и сравнение их с контрольными сигналами, записанными в накопитель 4 вмест е с информационным словом, на основании этого формирует единичные сигналы в случаях отказов разрядов накопителя 4. Сигнагы отказа управляют коммутаторами 2 таким образом, что старшие раз- .ряды информационного слова записываются в работоспособные разряды на- копителя 4, в результате чего-сохраняется максимально возможная точность записываемого в накопитель 4 информационного слова. 1 ил. 2 табл. i (Л оо 00 СА ОО к иС

О

О

Продолжение табл.1

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для программируемой задержки информации | 1984 |

|

SU1193653A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-13—Подача