со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для отладки программ | 1985 |

|

SU1280637A1 |

| Устройство для адресации | 1986 |

|

SU1361564A1 |

| Устройство сопряжения процессора с многоблочной памятью | 1989 |

|

SU1702383A1 |

| Устройство адресации оперативной памяти | 1985 |

|

SU1262497A1 |

| Устройство для сопряжения | 1987 |

|

SU1462331A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Устройство для параллельного обмена информацией | 1983 |

|

SU1164688A1 |

Изобретение относится к вычислительной технике и может быть использовано для увеличения объема оперативной памяти при построении цифровых систем обработки данных на базе мини-(микро)-ЭВМ. Цель изобретения - повьшение надежности за счет введения контроля на исправность. Устройство содержит регистр 1, дешифратор 2 блоков памяти, дешифратор 3 адреса, 9хему 4 сравнения и элемент 5 И. В регистр 1 заносится номер выбираемого блока памяти. При наличии логической единицы в старшем разряде выхода регистра 1 на выходе дешифратора 2 появляется сигнал ОЗУ-i. Контроль записи в регистр 1 осуществляется на схеме 4 сравнения. Если информация на входе и выходе регистра 1 различна, то устройство не вырабатывает сигнал ответа-на выходе элемента И 5, сообщая процессору о не- .исправности. 2 ип. $ (Л

Фиг. 7

114

Изобретение относится к вычислительной технике и может быть использовано для увеличения объема оперативной памяти при построении цифровых систем обработки данных на базе мини-(микро)-ЭВМ,

Цель изобретения - повьшекие надежности за счет введения контроля на исправность с

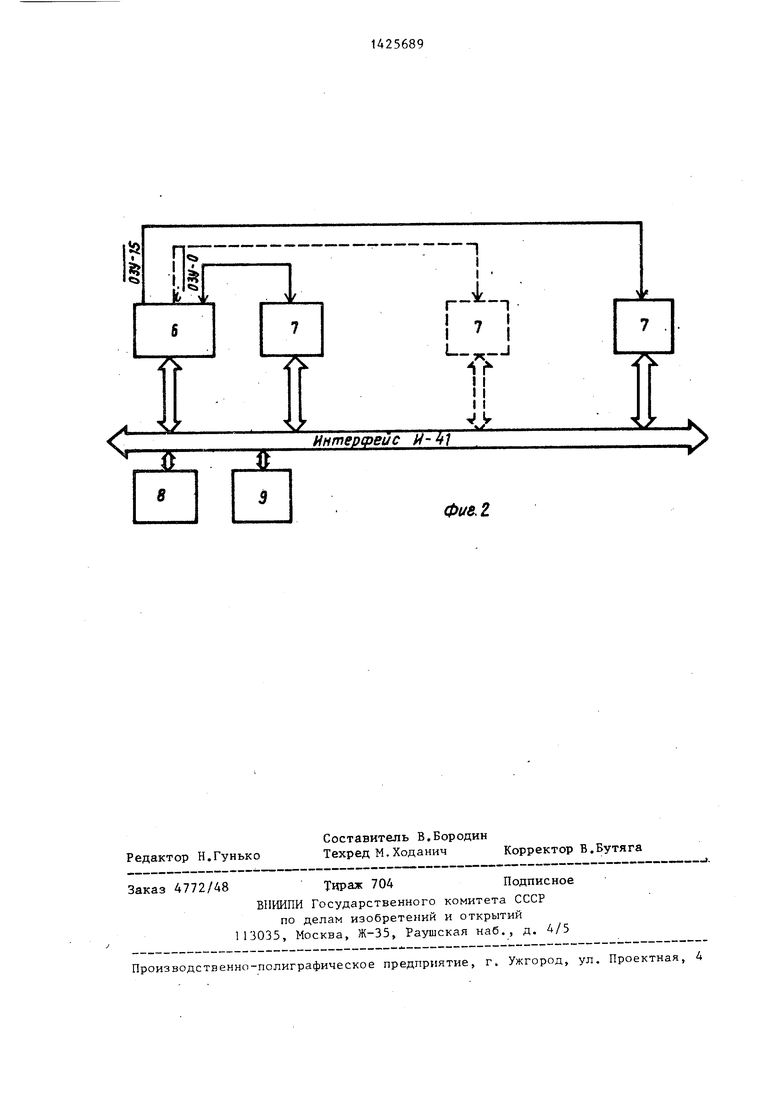

На фиг.1 показана функциональная схема устройства управления блоками памяти} на фиг,2 - возможное приме нение предлагаемого устройства

Устройство содержит регистр 1 Д шифратор 2 блоков памяти,, дешифратор 3 адреса, схему 4 сравнения и эле мент 5 Ио

На фиг,2 показаны устройство 6 управления блоками памяти, блоки 7

памяти, процессор 8, блок 9 памяти„

При применении предлагаемого устройства блок 9 памяти имеет индиви дуальное адресное пространство в адресном пространстве мини«-ЭВМ, например от 0000 до 7FFF, Остальные блоки 7 памяти, подключенные к устройству 6j имеют одни и те же адреса в адресном пространестве мини-ЭВМ например от 8000 до FFFF,

Выбор блоков 7 памяти осуществляется следующим образом.

Процессор 8 заносит информацию о выбираемом блоке 7 памяти в регистр 1, которьй имеет свой адрес в адресном пространстве , Если в старший разряд регистра 1 занесена логическая единица то разрешается выбор дешифратором 2 блока 7 памятив Если в старший разряд регистра 1 занесен логический ноль, то выбор дешифратором 2 блока 7 памяти запрещена. При записи процессора в регистр 1 номера выбираемого блока 7 памяти осзпц ствляется контроль записи номера блока памяти через схему 4 сравнее

0

и выходе регистра 1 не совпадают, на выходе элемента И 5 не формируется сигнал ответа,, отсутствие которого сообщает процессору о неисправности устройства,

К процессору может быть подключено несколько устройств б, регистры 1 которых имеют разные адреса в адресном пространстве микро-ЭВМ,

Формула изобретения

Устройство управления блоками памяти, содержащее регистр дешифратор

блоков памяти, деш1- фратор адреса и элемент И, информационный выход де

шифратора адреса являетсй адресным входом ус тройства J информационньвй

вход регистра является информационным входом устройства, выход дешифратора адреса соединен с входом стробирова- ния регистра, выход младших разрядов которого соединен с информационным входом дешифратора блоков памяти, управляющий вход которого соединен с выходом старшего разряда регистра, выходы дешифратора блоков памяти являются выходами выборки блоков памяти устройства, отлич ающе- е с я тем, что, с целью повышения надежности за счет введения контроля на исправность в него введена схема сравнения, первый вход схемы сравнения соединен с информационным входом регистра, выход которого соединен с вторым входом схемы сравнения, выход которой соединен с первым входом эле мента И, выход которого является выходом контроля на исправность устройства, выход дешифратора адреса соединен с вторым входом элемента И, вход сброса регистра является входом сброса устройства, управляющий вход де- шифратора адреса соединен с входом записи в устройство.

| Устройство для сопряжения процессора с многоблочной памятью | 1980 |

|

SU951315A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Черняк А.Ю | |||

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1988-09-23—Публикация

1987-02-17—Подача