17

О5

ы

315

Изобретение относится к вычислительной технике и может быть использовано в качестве запоминающего устройства при обработке информации в порядке ее поступления от абонентов, например, в ЭВМ при выполнении функций обслуживания большого числа периферийных устройств в мультиплексорах передачи данных для накопле- ния дискретной информации, поступающей из каналов связи, или в адаптерах локальных сетей ЭВМ.

Цель изобретения - расширение области применения за счет обеспе- чения работы в режиме с предварительным накоплением блока даннь1х произвольной дпины.

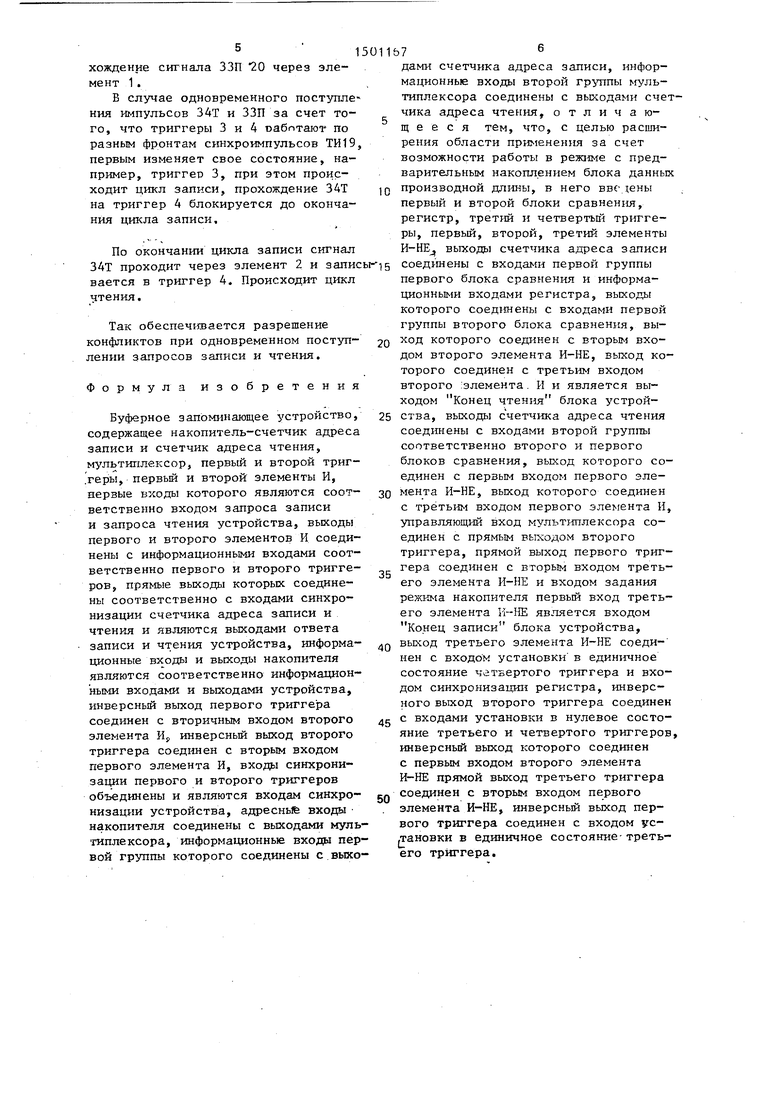

На чертеже показана структурная схема устройства.

Устройство содержит первый 1 и второй 2 элементы И, первый 3, второй 4, третий 5, четвертый 6 триггеры, первый 7, второй 8, третий 9 элементы И-НЕ, регистр 10, первый 11 и второй 12 блоки сравнения, счет- чик адреса записи 13 и чтения 14, мультиплексор 15, накопитель 16, информационные 17 входы и выходы 18 устройства, вход синхронизации 19, вход 20 запроса записи 20, вход 21 запроса чтения, вход 22 конец записи блока, выход 23 ответа записи, выход 24 ответ чтения, выход 25 конец чтения блока.

Коэффициенты пересчета счетчиков 13 и 14 одинаковы и равны информационной емкости накопителя liB, которая в свою очередь должна превышать максимальную длину блока данных Триггеры 3 и 4 переключаются по разным фронтам сигнала 19. Триггеры 5 и 6 имеют инверсные входы асинхронной установки и сброса. Регистр 10 и счетчики 13 и 14 срабатьшают по отрицательному фронту синхросигналов

Устройство работает следующим образом;

В исходном состоянии регистр, а также все триггеры и счетчики сброшены. Процесс зз-писи и считывания синхронизируется сигналом ТИ 19 с периодом повторения имйульсов, равным длительности времени записи в нако- питель 16. На адресный вход накопителя поступает содержимое счетчика 13, на вход W/R - уровень логического О. На выход 25 устройства посту

5

0

5 0 5

0 5

0

,

74

пает сигнал логического О, индицирующий отсутствие в накопителе 16 предварительно подготовленного блока данных. Прохождение импульса 34Т 21 через элемент 2 блокировано.

В процессе работы ВЗУ на входы 20 и 21 могут независимо поступать: t импульс ЗЗП, импульс 341, оба импульса ЗЗП и 341.

В случае поступления импульса ЗЗП он проходит через разблокированный элемент И 1 и запоминается в триггере 3. При этом блокируется прохождение 34Т через элемент 2, устанавливается триггер 5, на вход W/R накопителя подается сигнал логической 1 - сигнал записи, выдается ответный сигнал ОЗП 23 во внешнюю среду, после чего возможно снятие входного сигнапа ЗЗП. Затем пассивный уровень сигнала ЗЗП запоминается в триггере 3.

При этом прекращается запись числа в накопитель 16, наращивается счетчик 13, который теперь указывает на адрес следующего цикла записи, разблокируется элемент 2.

Установленный триггер 5 разрешает прохождение сигнала с блока 11 сравнения через элемент 7, который блокирует вход ЗЗП в случае заполнения накопителя после цикла записи.

Если в цикле записи подавался сигнал, КЗБЛ 22 (запись последнего слова блока данных), то по сигналу с выхода элемента 9 в регистр 10 защелкивается адрес последнего цикла записи, устанавливается триггер 6, вследствие чего разблокируется элемент 2 и вьщается сигнал на выход 25, индицирующий о наличии готового блока данных в на копителе 16. 1

В случае поступления импульса

34Т на вход 21 происходит считьша- ние числа по адресу, определяемому счетчиком 14. Цикл чтения аналогичен циклу записи. К концу цикла чтения счетчик 14 наращен; триггер 6 сброшен, вследствие чего выход блока 12 сравнения подключен через элемент 8 по входу элемента 2 и после считьтания последнего слова предварительно подготовленного блока данных блокирует прохождение сигнала 34Т, а также вызьгоает появление сигнала К4БП (конец чтения блока) 25; триггер сброшен, вследствие чего разрешено прЪ 1 хождение сигнала ЗЗП 20 через элемент 1 .

В случае одновременного поступле- ния импульсов 34т и ЗЗП за счет того, что триггеры 3 и 4 сабптагот по разным фронтам синхроимпульсов ТИ19 первым изменяет свое состояние, например, триггер 3, при этом происходит цикл записи, прохождение 34Т на триггер 4 блокируется до окончания цикла записи.

По окончании цикла записи сигнал 34т проходит через элемент 2 и запис вается в триггер 4. Происходит цикл чтения.

Так обеспеч1шается разрешение конфликтов при одновременном поступ- лении запросов записи и чтения.

Формула изобретения

Буферное запоминающее устройство, содержащее накопитель-счетчик адреса записи и счетчик адреса чтения, мультиплексор, первый и второй триг- .геры, первый и второй элементы И, первые входы которого являются соот- ветственно входом запроса записи и запроса чтения устройства, выходы первого и второго элементов И соединены с информационными входами соответственно первого и второго тригге ров, прямые выходы которых соединены соответственно с входами синхронизации счетчика адреса записи и чтения и являются выходами ответа записи и чтения устройства, информа- ционные входы и вьсходы накопителя являются соответственно информационными входами и выходами устройства, инверсный выход первого триггера соединен с вторичным входом второго элемента Ир инверсный выход второго триггера соединен с вторым входом первого элемента И, входы синхронизации первого и второго триггеров объединены и являются входам синхро- низации устройства, адресные входы накопителя соединены с выходами мультиплексора, информационные входы первой группы которого соединены с выхо

Q

д

0

5 о Q 5

5

676

дами счетчика адреса записи, информационные входы второй гр | Т1Пы мультиплексора Соединены с выходами счетчика адреса чтения, отличающееся тем, что, с целью расширения области применения за счет возможности работы в режиме с предварительным накоплением блока данных производной длины, в него введены первый и второй блоки сравнения, регистр, третий и четвертьй триггеры, первый, второй, третий элементы И-HEj, выходы счетчика адреса записи соедршены с входами первой группы первого блока сравнения и информационными входами регистра, выходы которого соединены с входами первой группы второго блока сравнения, выход которого соединен с вторым входом второго элемента И-НЕ, выход которого соединен с третьим входом второго :элемента. И и является выходом Конец чтения блока устройства, вьосоды с четчика адреса чтения соединены с входами второй группы соответственно второго и первого блоков сравнения, выход которого соединен с первым входом первого элемента И-НЕ, выход которого соединен с третьим входом первого элемента И, управляющий вход мультиплексора соединен с прямым выходом второго триггера, прямой выход первого триггера соединен с вторым входом третьего элемента И-ИЕ и входом задания режима накопителя первый вход третьего элемента li-HE является входом Конец записи блока устройства, выход третьего элемента И-НЕ соеди- нен с входом установки в единичное состояние ччгтвертого триггера и входом синхронизации регистра, инверсного выход второго триггера соединен с входами установки в нулевое состояние третьего и четвертого триггеров, инверсный выход которого соединен с первым входом второго элемента И-НЕ прямой выход третьего триггера соединен с вторьм входом первого элемента И-НЕ, инверсньш выход первого триггера соединен с входом ус- /гановки в единичное состояние- третьего триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1388951A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1580442A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1290339A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство адресации для канала прямого доступа к памяти | 1985 |

|

SU1283763A1 |

Изобретение относится к вычислительной технике и может быть использовано при обработке информации в порядке ее поступления от абонентов, например, в ЭВМ при выполнении функций обслуживания большого числа периферийных устройств, в мультиплексорах передачи данных для накопления дискретной информации, поступающей из каналов связи, или в адаптерах локальных сетей ЭВМ. Целью изобретения является - расширение области применения за счет обеспечения работы в режиме с предварительным накоплением блока данных произвольной длины. Буферное запоминающее устройство содержит первый 1 и второй 2 элементы И, триггеры 3-6, первый 7, второй 8 и третий 9 элементы И-НЕ, регистр 10, первый 11 и второй 12 блоки сравнения, счетчики адреса записи 13 и адреса чтения 14, мультиплексор 15 и накопитель 16. 1 ил.

| Буферное запоминающее устройство | 1979 |

|

SU822287A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1111202A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-08-15—Публикация

1987-04-14—Подача