Изобретение относится к вычислительной технике и может быть использовано в устройствах управления помощью ЭВМ, в частности полупровод- никовой динамической памятью, выпол ненной на БИС.

Цель изобретения - упрощение устройства и повышение его быстродействия за счет уменьшения среднего вре- мани ожидания на удовлетворение внешнего запроса.

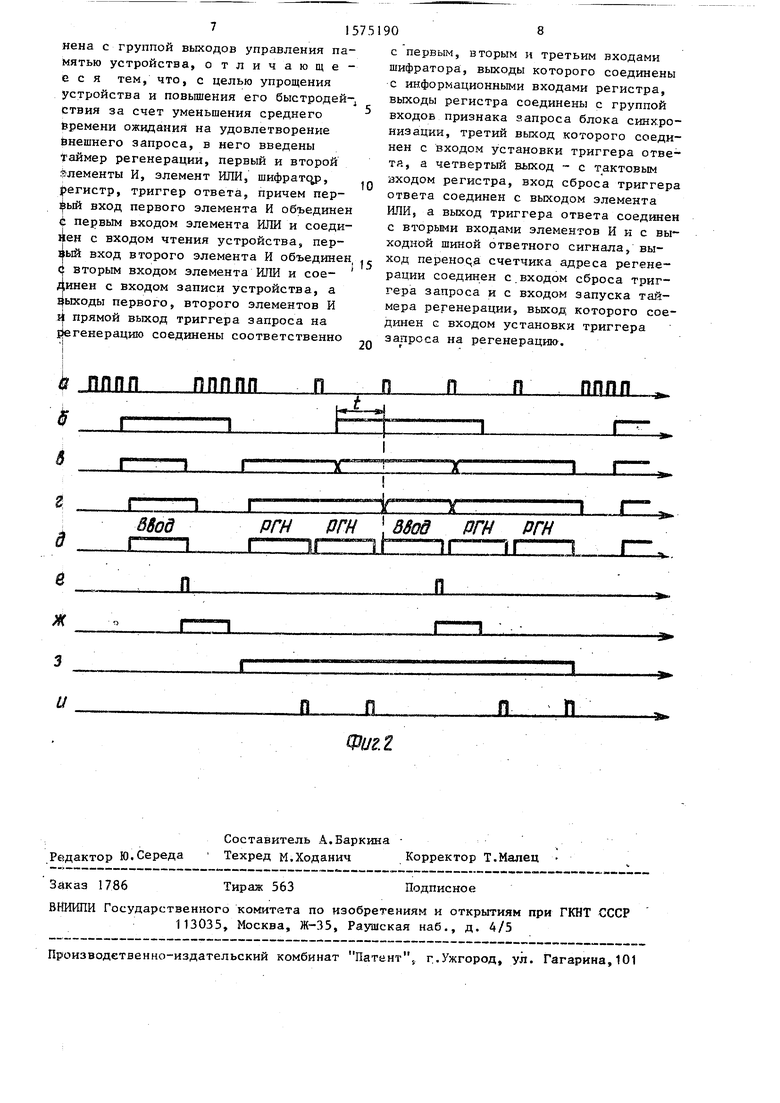

На фиг.1 приведена структурная схема предлагаемого устройства для управления динамической памятью; на фиг.2 - временная диаграмма работы устройства.

Устройство содержит таймер 1 регенерации,; триггер 2 запроса на реге нерацию, блок 3 синхронизации, муль- типлексор 4 адреса, счетчик 5 адреса регенерации, элементы И 6 и 7, элемент ИЛИ 8, шифратор 9, регистр 10, триггер П ответа, вход 12 чтения, вход 13 записи, группу выходов 14 уп равления памятью, группу выходов 15 адреса памяти, группу входов 16 адреса памяти, выход 17 ответного сигнала.

На временной диаграмме (фиг.2) вс сигналы условно показаны положительной полярности. При этом на диаграмме приняты следующие обозначения: тактовый вход а регистра 10; сигнал б внешнего запроса на входе 12 чте- ния; информационные входы в регистра 10, сигналы на которых изменяются в зависимости от наличия того или иного запроса; сигналы г на выходе регистра 10; время д, в течение ко- торог.о блок 3 синхронизации формирует цикл обращения к памяти по внешнему запросу или по запросу на регенерацию памяти; сигнал е цикла обращения к памяти по внешнему запросу на третьем выходе блока синхронизации; сигнал ж на инверсном выходе триггера 11, который является ответным сигналом и поступает на вторые входы элементов И 6 и 7; сигнап з на прямом выходе триггера 2 запроса на регенерацию; сигнал и конца цикла регенерации на втором выходе блока 3 синхронизации.

Устройство работает следующим образом.

Внешний сигнал чтения является внешним запросом на организацию цикла чтения данных из памяти. Внешний

0 5 0 5 Q

5

сигнал записи является внешним запросом на организацию цикла записи данных в память. Сигнал на выходе триггера 2 запроса на регенерацию является запросом на регенерацию памяти. В исходном состоянии при отсутствии внешних запросов и запроса на регенерацию памяти на входах шифратора 9 и соответственно на его выходах, а также на информационных входах регистра 10 и на его выходах присутствуют пассивные уровни сигналов. Блок 3 синхронизации формирует сигналы только на своем четвертом выходе, которые являются сигналами опроса, поступающими на тактовый вход регистра 10. При этом триггер 11 находится в нулевом состоянии, и на его инверсном выходе присутствует уровень 1.

Входы элементов И 6 и 7 так подключены к шифратору 9, что имеют более высокий приоритет по сравнению с третьим его входом, соединенным с прямым выходом триггера 2 запроса на регенерацию. Шифратор 9 формирует на выходе комбинацию сигналов, соответствующую сигналу на каждом его входе. Если на первом входе (или втором, так как они не могут присутствовать одновременно) появился сигнал и сигнал на третьем, то на выходе шифратора 9 будет присутствовать комбинация сигналов, соответствующая входному сигналу на первом входе.

При появлении одного из внешних запросов на входах 12 или 13 на выходе соответствующего элемента И 6 или 7 появится сигнал, который, поступая на один из входов шифратора 9, вызовет на его выходе соответ- ствуюшу о комбинацию сигналов, которая, попадая на инфорационные входы регистра 10, будет в нем зафиксирована импульсом опроса, поступающим с четвертого выхода блока 3 синхронизации на тактовый вход регистра 10.

При появлении сигналов на выходе регистра 10 и соответственно на группе входов признака запроса блока 3 синхронизации блок синхронизации прекращает выдачу сигналов опроса и начинает формирование сигналов управления мультиплексором 4 адреса (на первом своем выходе) и памятью, которые появятся на выходах 14 в соответствии с поступившим запросом.

5

По окончании цикла обращения к памяти на третьем выходе блока 3 синхронизации формируется сигнал конца цикла, который поступает на установочный вход триггера П. На его инверсном выходе появится ответный сигнал, который поступает на выход 17 и на вторые входы элементов И 6 и 7, запрещая прохождение внешних сигналов запроса на вход шифратора 9. Это необходимо для того, чтобы в регистр 10 повторно не записывалась предыдущая комбинация сигналов, соответствующая удовлетворенному запросу так как после сигнала конца цикла блок 3 синхронизации опять начинает формирование сигналов опроса на своем четвертом выходе, поступающих на тактовый вход регистра 10. Когда с входов 12 или 13 снимается сигнал запроса, то на выходе элемента ИЛИ 8 появляется сигнал, который, поступая на вход сброса триггера 11, устанавливает его в нулевое состояние, при котором снимается ответный сигнал с выхода 17 и запрещающий сигнал с вторых входов элементов И 6 и 7.

Когда таймер 1 регенерации, сформировав временный интервал, выработает на своем выходе короткий импульс, этот импульс, поступая на установочный вход, установит триггер 2 запроса на генерацию в единичное состояние, и сигнал с его инверсного выхода поступит на третий вход шифратора 9.

При отсутствии внешних запросов на входах 12 и 13 на выходе шифратора появится комбинация сигналов, со- Ьтветствующая запросу на регенерацию памяти. Блок 3 синхронизации сформирует соответствующие сигналы управления мультиплексором 4 адреса и памятью и в конце цикла сформирует сигнал на своем втором выходе, который, поступая на счетный вход счетчика 5 адреса регенерации, увеличит его содержимое на единицу. При этом на третьем выходе блока 3 синхронизации сигнал не формируется, а сигнал опроса с его четвертого выхода поступает на тактовый вход регистра 10 и если на информационных входах комбинация сигналов не изменилась, то цикл регенерации памяти повторяется.

Работа в такой последовательности продолжается до тех пор, пока

10

751906

счетчик 5 адреса регенерации не переполнится, в этом случае на втором выходе счетчика появится сигнал переполнения, который поступает на

5 вход сброса триггера 2 запроса на регенерацию, устанавливает его в нулевое состояние, что снимает с третьего входа шифратора запрос на регенерацию памяти и снова запускает таймер 1 регенерации.

Если в регистре 10 зафиксирован внешний запрос, то запрос на регенерацию будет удовлетворяться только после завершения начатого цикла. При установленном запросе на регенерацию пямяти на третьем входе шифратора 9 пришедший внешний запрос на первый или второй вход шифратора отменит регенерацию памяти, поскольку внешний запрос имеет более высокий приоритет, то только после завершения начатого цикла.

На временной диаграмме (фиг.2)

25 видно, что несмотря на наличие запроса 3 на регенерацию при появлении внешнего запроса (д) он удовлетворяется с минимальной задержкой, которая всегда меньше времени одного цик- ла регенерации.

Эти столкновения возможны только в период времени, отведенный на регистрацию и определяемый таймером. Количество столкновений зависит от интенсивности поступления внешних за35 просов. За счет того, что приоритет внешнего запроса выше, чем запрос на регистрацию, то снижается среднее время ожидания удовлетворения внешнего запроса.

15

20

40

Формула изобретения Устройство для управления динамической памятью, содержащее триггер запроса не регенерацию, блок синхро45 низации, мультиплексор адреса, счетчик адреса регенерации, причем группа его выходов соединена с первой группой информационных входов мультиплексора адреса, выходы которого сое50 динены с группой выходов адреса памяти устройства, группа входов адреса памяти которого соединена с второй группой информационных входов мультиплексора адреса, управляющий вход

55 которого соединен с первым выходом блока синхронизации, второй выход ко- торого соединен со счетным входом счетчика адреса регенерации, а группа выходов блока синхронизации соеди715

нена с группой выходов управления памятью устройства, отличающееся тем, что, с целью упрощения устройства и повышения его быстродей-, ствия за счет уменьшения среднего времени ожидания на удовлетворение внешнего запроса, в него введены Таймер регенерации, первый и второй элементы И, элемент ИЛИ, шифратор, регистр, триггер ответа, причем пер- $ый вход первого элемента И объединен с первым входом элемента ИЛИ и соединен с входом чтения устройства, пер- ьй вход второго элемента И объединен, 4 вторым входом элемента ИЛИ и сое- 4инен с входом записи устройства, а цыходы первого, второго элементов И и прямой выход триггера запроса на

регенерацию соединены соответственно

|

8

,

0

с первым, вторым и третьим входами шифратора, выходы которого соединены с информационными входами регистра, выходы регистра соединены с группой входов признака запроса блока синхронизации, третий выход которого соединен с входом установки триггера ответа, а четвертый выход - с тактовым входом регистра, вход сброса триггера ответа соединен с выходом элемента ИЛИ, а выход триггера ответа соединен с вторыми входами элементов И и с выходной шиной ответного сигнала, выход переноца счетчика адреса регенерации соединен с входом сброса триггера запроса и с входом запуска таймера регенерации, выход которого соединен с входом установки триггера запроса на регенерацию.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для управления обслуживанием запросов | 1990 |

|

SU1709315A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления памятью ЭВМ, в частности полупроводниковой динамической памятью, выполненной на БИС. Цель изобретения - упрощение устройства и повышение его быстродействия за счет уменьшения среднего времени ожидания на удовлетворение внешнего запроса. Устройство содержит таймер 1 регенерации, триггер 2 запроса на регенерацию, блок 3 синхронизации, мультиплексор 4 адреса, счетчик 5 адреса регенерации, элементы И 6 и 7, элемент ИЛИ 8, шифратор 9, регистр 10, триггер 11 ответа. 2 ил.

в

&

38од

L

X

r-t-г-

РГИ РГН двод РГН РГН

ж

п

1C

п

ж

3

и

п

Составитель А.Баркина - Редактор Ю.Середа Техред М.Ходанич Корректор Т.Малец

Заказ 1786

Тираж 563

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

1C

-%..

п

л

л

-э

Ql/lZ

Подписное

| Устройство для управления полупроводниковой памятью | 1977 |

|

SU746515A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления оперативной динамической памятью | 1985 |

|

SU1251174A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1377909A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-06-30—Публикация

1988-08-01—Подача