(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Дешифратор | 1989 |

|

SU1644222A1 |

| Полупроводниковое запоминающее устройство | 1979 |

|

SU879651A1 |

| Устройство для записи информации в МДП динамический-матричный накопитель | 1982 |

|

SU1091222A1 |

| Формирователь импульсов | 1985 |

|

SU1374417A1 |

| ДЕШИФРАТОР АДРЕСА | 1989 |

|

SU1637568A1 |

| Дешифратор для запоминающего устройства с резервированием | 1984 |

|

SU1213503A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании запоминающих устройств в качестве дешифратора адресов строк и столбцов. Целью изобретения является повышение быстродействия дешифратора. Для этого тактовые входы 9-11 ключевых элементов 1 и элементов И первой 2 и второй 3 групп выполняют раздельными. При этом разряд емкостей нагрузки и затворов ключевых транзисторов 15 происходит через открытые транзисторы 14 и 18 соответственно. 2 з.п.ф-лы, 2 ил.

Фг/г.7

Изобретение относится к вычислительной технике и может быть исполь- овано при проектировании запоминаю- DtHx устройств в качестве дешифратора, адресов строк и столбцов.

Цель изобретения - повышение быстродействия дешифратора.

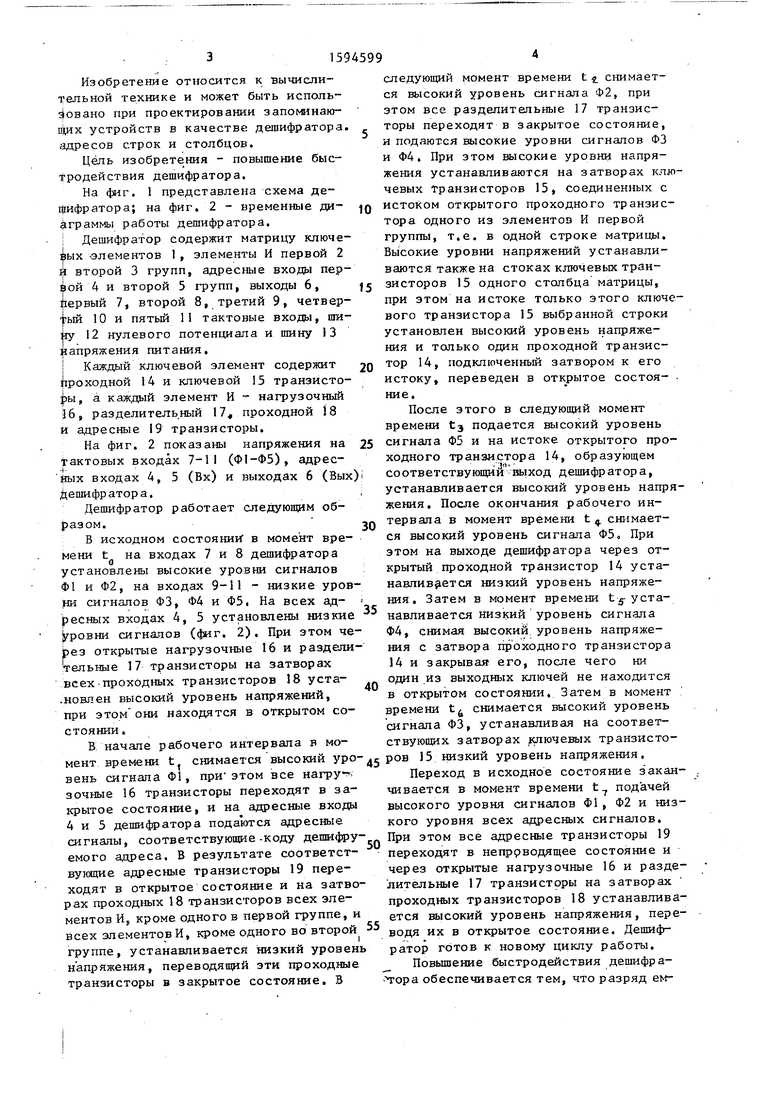

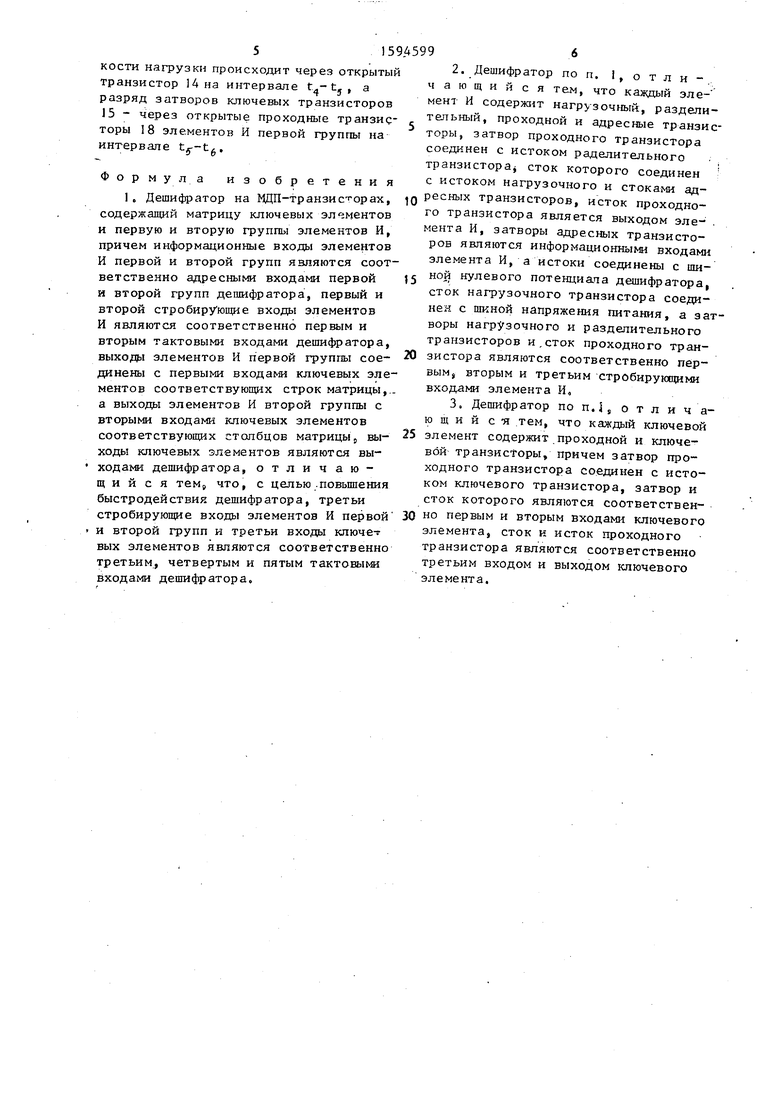

На фиг. 1 представлена схема де фифратора; на фиг, 2 - временные диаграммы работы дешифратора, I Дешифратор содержит матрицу ключе- $ых -элементов 1 , элементы И первой 2 $ второй 3 групп, адресные входы пер- фой 4 и второй 5 групп, выходы 6, tiepBbm 7, второй 8, третий 9, четвер- 10 и пятый 11 тактовые входы, ши- ky 12 нулевого потенциала и шину 13 Напряжения питания, Каждый ключевой элемент содержит йроходной 14 и ключевой 15 транзисто- jfibif а каждый элемент И - нагрузочный |6, разделитель.ный 17, проходной 18 и адресные 19 транзисторы.

На фиг, 2 показаны напряжения на тактовых входах 7-М (Ф1-Ф5), адрес- йых входах 4, 5 (Вх) и выходах 6 (Вых) ,ешифратора.

Дешифратор работает следующим образом,

В исходном состоянииг в момент времени t на входах 7 и 8 дешифратора

1594599

следующий момент времени t снимается высокий уровень сигнала Ф2, при этом все разделительные 17 транзисторы переходят в закрытое состояние, и подаются высокие уровни сигналов ФЗ и Ф4, При этом высокие уровни напряжения устанавливаются на затворах клда- чевых транзисторов 15, соединенных с

Q истоком открытого проходного транзистора одного из элементов И первой группы, т,е. в одной строке матрицы. Высокие уровни напряжений устанавливаются также на стоках ключевых транJC зисторов 15 одного столбца матрицы, при этом на истоке только этого ключевого транзистора 15 выбранной строки установлен высокий уровень напряже- ьшя и только один проходной транзис2Q тор 14, подключенный затвором к его истоку, переведен в открытое состоя- ние.

После этого в следующий момент времени t3 подается высокий уровень

25 сигнала Ф5 и на истоке открытого проходного транзистора 14, образующем

соответствующий выход дешифратора,

; устанавливается высокий уровень напряжения. После окончания рабочего ин,( тервала в момент времени t ( снимается высокий уровень сигнала Ф5о При этом на выходе дешифратора через от; крытый проходной транзистор 14 уста- навлив ется низкий уровень напряжения. Затем в момент времени 15-устанавливается низкий уровень сигнала Ф4, снимая высокий уровень напряжения с затвора проходного транзистора 14 и закрывая его, после чего ни один .из выходных ключей не находится в открытом состоянии. Затем в момент времени t снимается высокий уровень сигнала ФЗ, устанавливая на соответствующих затворах ключевых транзисто40

установлены высокие уровни сигналов Ф1 и Ф2, на входах 9-11 - низкие уровни сигналов ФЗ, Ф4 и Ф5. На всех а,ц- ресных входах 4, 5 установлены низкие Дровни сигналов (фиг, 2), При этом че- Ьеэ открытые нагрузочные 16 и разделительные 17 транзисторы на затворах всех-проходных транзисторов 18 уста- .новлен высокий уровень напряжений, при этом они находятся в открытом состоянии.

В начале рабочего интервала в момент времени t. снимается высокий 15 низкий уровень напряжения, вень сигнала Ф1, при этом все нагру Переход в исходное состояние заканзочные 16 транзисторы переходят в за- чивается в момент времени t подачей крытое состояние, и на адресные входы высокого уровня сигналов Ф1, Ф2 и низ- 4 и 5 дешифратора подаются адресныекого уровня всех адресных сигналов,

сигналы, соответствующие-коду деши(})ру- При этом все адресные транзисторы 19 емого адреса, В результате соответст- переходят в непррводящее состояние и вукщие адресные транзисторы 19 пере-через открытые нагрузочные 16 и раздеходят в открытое состояние и на затво- лительные 17 транзисторы на затворах pax проходных 18 транзисторов всех эле-проходных транзисторов 18 устанавливаментов И, кроме одного в первой группе, и ется высокий уровень напряжения, пере- всех элементов И, кроме одного во второй водя их в открытое состояние, Дешиф- группе, устанавливается низкий уровень напряжения, переводящий эти проход;ные транзисторы в закрытое состояние, В

ратор готов к новому циклу работы.

Повышение быстродействия дешифра- -Тора обеспечивается тем, что разряд ем ется высокий уровень напряжения, пере водя их в открытое состояние, Дешиф-

ратор готов к новому циклу работы.

Повышение быстродействия дешифра- -Тора обеспечивается тем, что разряд ем51594599

кости нагрузки происходит через открытый транзистор 14 на интервале разряд затворов ключевых транзисторов J5 - через открытые проходные транзисторы 18 элементов И первой группы на интервале .

Фор мула

зобретени

адресные транзисторы, затвор проходного транзистора соединен с истоком раделительного транзистора, сток которого соединен с истоком нагрузочного и стоками ад- 1. Дешифратор на ВДП-транзисборах, д транзисторов, исток проходно- содержащий матрицу ключевых элементов ° транзистора является выходом эл и первую и вторую группы элементов И, мента И, затворы адресных транзисто- причем информационные входы элементовР°в являются информационными входами

И первой и второй групп являются соот- элемента И, а истоки соединены с ши- ветственно адресными входами первой }5 °i нулевого потенциала дешифратора

и второй групп дешифратора, первый --

второй стробирующие входы элементов И являются соответственно первым и вторым тактовыми входами дешифратора, выхода элементов И первой группы сое20

сток нагрузочного транзистора соединен с шкной напряжения питания, а затворы нагрузочного и разделительного транзисторов и.сток проходного транзистора являются соответственно первым, вторым и третьим стробируюощми входами элемента И,

дине1л 1 с первыми входами ключевых элементов соответствующих строк матрицы,.. а выходы элементов И второй группы с вторыми входами ключевых элементов соответствующих столбцов матрицы выходы ключевых элементов являются выходами дешифратора, отличающийся TeMj что, с целью .повьшения быстродействия дешифратора, третьи

стробирующие входы элементов И первой 30 но первым и вторым входами ключевого и второй групп и третьи входы ключе-элемента, сток к исток проходного

вых элементов являются соответственно транзистора являются соответственно третьим, четвертым и пятым тактовымитретьим входом и выходом ключевого

входами дешифратора,элемента.

сток нагрузочного транзистора соединен с шкной напряжения питания, а за воры нагрузочного и разделительного транзисторов и.сток проходного транзистора являются соответственно первым, вторым и третьим стробируюощми входами элемента И,

3, Дешифратор по n.i, о т л и ч а- ю щ и и с -я тем, что каждый ключевой 25 элемент содержит.проходной и ключевой транзисторы, причем затвор проходного транзистора соединен с истоком ключевого транзистора, затвор и сток которого являются соответствен2. Дешифратор по п. 1, о т л и - ч а ю щ и и с я тем, что кавдый эле- мент И coдepж,iт нагрузочный, разделительный, проходной и

адресные транзисторы, затвор проходного транзистора соединен с истоком раделительного транзистора, сток которого соединен с истоком нагрузочного и стоками ад- транзисторов, исток проходно- ° транзистора является выходом эл элемента И, а истоки соединены с ши- °i нулевого потенциала дешифратора

--

о первым и вторым входами ключевого лемента, сток к исток проходного

сток нагрузочного транзистора соединен с шкной напряжения питания, а затворы нагрузочного и разделительного транзисторов и.сток проходного транзистора являются соответственно первым, вторым и третьим стробируюощми входами элемента И,

3, Дешифратор по n.i, о т л и ч а- ю щ и и с -я тем, что каждый ключевой элемент содержит.проходной и ключевой транзисторы, причем затвор проходного транзистора соединен с истоком ключевого транзистора, затвор и сток которого являются соответствен.1 I

tp ir tt

«3и

.2

Редактор О,Головач

Составитель А,Дерюгин,

Техред М.Дидык. Корректор Т.Палий

Заказ 2833

Тираж 487

ВНИРШИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35„ Раушская наб., д. 4/5

-«- -«-ie-.e,-.«.,«.«

в.-мв,,

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

ts ts t7

Подписное

| IEEE journal of Solid State Circiiits, vol | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Паровозный поршень, останавливающийся при езде без пара | 1924 |

|

SU839A1 |

| Каган Б.М., Каневский М.М | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| -M | |||

| i Энергия, 1974, с | |||

| Питательное приспособление к трепальным машинам для лубовых растений | 1922 |

|

SU201A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-09-23—Публикация

1987-10-02—Подача