Изобретение относится к вычислительной технике и может быть использовано в системах обработки дискретной информации

Цель изобретения - повышение быстродействия.

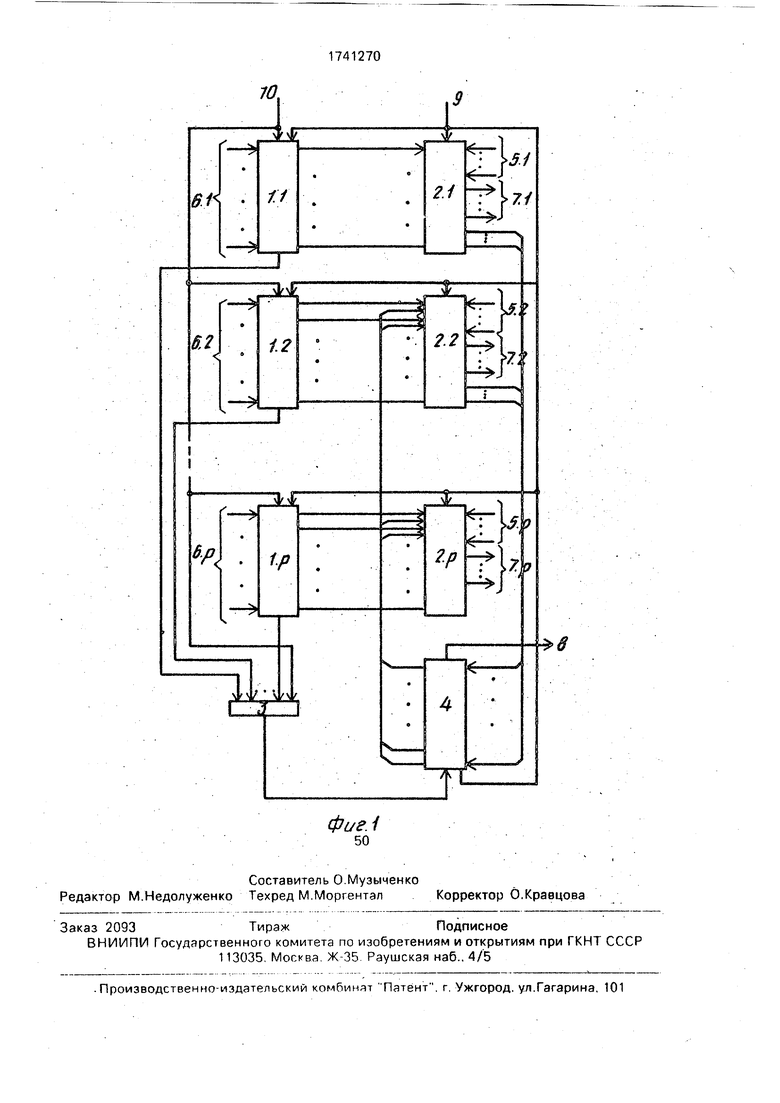

На фиг. 1 представлена структурная схема преобразователя кода системы счисления с одним основанием в код системы счисления с другим основанием; на фиг. 2 - схема преобразователя для случая входного 12-разрядного двоично-десятичного и выходного двоичного кодов при

Преобразователь (фиг 1) содержит группу 1 блоков преобразования параллельного кода и последовательности импульсов 1 1- 1 р, группу 2 блоков подсчета единиц в выходном коде 2.1-2 р. элемент И 3, блок 4 преобразования параллельного кода в последовательности импульсов, информационные входы второй группы 5, информационные входы первой группы 6. выходы 7 преобразователя, выход 8 окончания работы, вход начальной установки 9. тактовый вход 10.

Блок 1.1 преобразования параллельного кода в последовательности импульсов (i

1р) соединен входами с инфбрмационными входами 6 I первой группы, выходами - с соответствующими счетными входами блока подсчета единиц в выходном коде 2.i, тактовым входом - с тактовым входом 10 преобразователя, входом сброса - с входом 9 начальной установки преобразователя, а выходом окончания работы - с i-м входом элемента И 3, (р+1)-й вход которого соединен с тактовым входом 10 преобразователя, а выход - с тактовым входом блока 4 преобразования параллельного кода в последовательности импульсов, соединенного информационными входами с выходами разрядов переполнения блоков подсчета единиц в выходном коде 2.1-2.(р-1). входом сброса - с

входом 10 начальной установки преобразователя выходом окончания работы - с выходом 8 окончания работы преобразователя, а выходами разрядов - со счетными входами вторых групп блоков 2.1-2.р подсчета единиц в выходном коде, блоки 2.1-2.р подсчета единиц в выходном коде группы соединены выходами разрядов результата .с информационными выходами 7.1-7.р преобразователя, входами сброса с входом 9 начальной

установки преобразователя, а информационными входами - с информационными входами второй группы 5 1-5.р преобразователя.

Блок 1.1 преобразования параллельного

кода в последовательности импульсов (фиг.2) содержит распределитель импульсов 12, группы элементов И 15, элементы ИЛИ 11.

Блок 4 преобразования параллельного

кода в последовательности импульсов 4 содержит распределитель импульсов 12 элементы И 15.

Блок 2. i подсчета единиц в выходном коде (фиг.2) содержит счетные триггеры TJ и

элементы ИЛИ 14.

Функционирование устройства происходит следующим образом.

Входной код подается на информационные входы 5.1-5-р второй группы и записывается в блоки 2.1-2.р подсчета единиц в выходном коде группы. Одновременно входной код подается на информационные входы 6.1-б.р первой группы и поступает на информационные входы блоков 1 1-1.р преобразования параллельного кода в последовательности 4импульсов. После установки блоков 2 группы на тактовый вход 10 устройства подаются тактовые импульсы, при этом блоки 1.1-1.р преобразования параллельного кода в последовательности импульсов преобразуют единичные сигналы на своих информационных входах в импульсы на соответствующих выходах, поступающие на

счетные входы первой группы блоков 2.1-2.р подсчета единиц в выходном коде группы, которые их подсчитывают. По окончании преобразования входного кода каждый из блоков 1.1 преобразования входного кода в последовательности импульсов формирует на своем выходе окончания работы единичный сигнал и самоблокируется, т.е. перестает формировать импульсы на своих выходах. При появлении единичных сигналов на выходах окончания работы всех блоков 1.1 преобразования параллельного кода в последовательности импульсов группы тактовые импульсы с входа 10 начинают проходить через элемент И 3 на тактовый вход блока 4 преобразования параллельного кода в последовательности импульсов, который преобразует коды с выходов разрядов переполнения блоков2.1-2.р-1 подсчета единиц в выходном коде в последовательности импульсов на соответствующих выходах, которые поступают на счетные входы второй группы блоков 2 2-2 р подсчета единиц в выходном коде группы, чем обеспечивается компенсация отсутствующих переносов между блоками 2 группы. По окончании работы блок 4.преобразования параллельного кода в последовательности импульсов самоблокируется и формирует на выходе окончания работы единичный сигнал, поступающий на выход 8 окончания работы устройства, свидетельствуя об окончании преобразования входного кода. Выходной код снимается с выходов 7.1-7.р блоков 2.1-2-р подсчета единиц в выходном коде группы.

Таким образом, предложенный преобразователь обеспечивает повышение быстродействия.

Формула изобретения Преобразователь кода системы счисления с одним основанием в код системы счисления с другим основанием, содержащий группу блоков преобразования параллельного кода в последовательности импульсов.

группу блоков подсчета единиц в выходном коде и элемент И, причем выходы окончания работы блоков преобразования параллельного кода в последовательности импульсов

5 группы и тактовый вход преобразователя соединены соответственно с входами элемента И, вход начальной установки преобразователя соединен с входами сброса блоков преобразования параллельного ко0 да в последовательности импульсов группы и с входами сброса блоков подсчета единиц в выходном коде группы, тактовый вход преобразователя соединен с тактовыми входами блоков преобразования параллельного

5 кода в последовательности импульсов группы, информационные входы которых соединены с соответствующими информационными входами первой группы преобразователя, о т л и ч а-ю щ и и с я тем, что. с целью повышения быстродействия, он содержит дополнительный блок преобразования параллельного кода в последовательности импульсов, причем выходы разрядов k-ro (k 1-р, р - количество параллельно преобразу- емых групп разрядов ехидного кода) блока преобразования параллельного кода в последовательности импульсов группы соединены с соответствующими счетными входами первой группы k-ro блока подсчета

0 единиц в выходном коде группы, выходы разрядов результата блоков подсчета единиц в выходном коде группы соединены соответственно с информационными выходами г,:у T -реобразователя, выход окон5 чан т р: С ;, « которого соединен с выходом гкен1Г|ч работы дополнительного блока r.feoJ. золения параллельного кода в по- следгч ательности импульсов, тактовый вхс :, м :.од сброса которого соединены со0 ответ ч аенно с выходом элемента И и с входом начальной установки преобразователя, информационные входы второй группы которого соединены с информационными входами соответствующих блоков подсчета

5 единиц в выходном коде группы, выходы разрядов переполнения блоков подсчета единиц в выходном коде, кроме р-ro, группы соединены соответственно с информационными входами дополнительного блока

0 преобразования параллельного кода в последовательности импульсов, выходы разрядов которого соединены соответственно со счетными входами вторых групп блоков подсчета единиц в выходном коде, кроме

5 -первого, группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода системы счисления с одним основанием в код системы счисления с другим основанием | 1990 |

|

SU1741269A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

| Пороговый элемент | 1986 |

|

SU1387185A2 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

| Преобразователь кода одной позиционной системы счисления в другую | 1980 |

|

SU960793A1 |

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обработки дискретной информации Цель изобретения - повышение быстродействия. Преобразователь содержит группу блоков 1.1-1-р преобразования па

| Преобразователь кодов | 1987 |

|

SU1462487A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1427574A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1992-06-15—Публикация

1990-01-02—Подача