00

ю о со ю ю

Изобретение относится к вычислительной технике и может быть использовано при создании информационно-управляющих систем с высокой скоростью передачи данных. . - . . .,-... - .- .- . ./- Цель изобретения - расширение области применения и повышение производительности системы за счет реализации двунаправленной передачи между центральным процессорным блоком и периферийными процессорными блоками с возможностью выбора периферийных процессорных блоков.

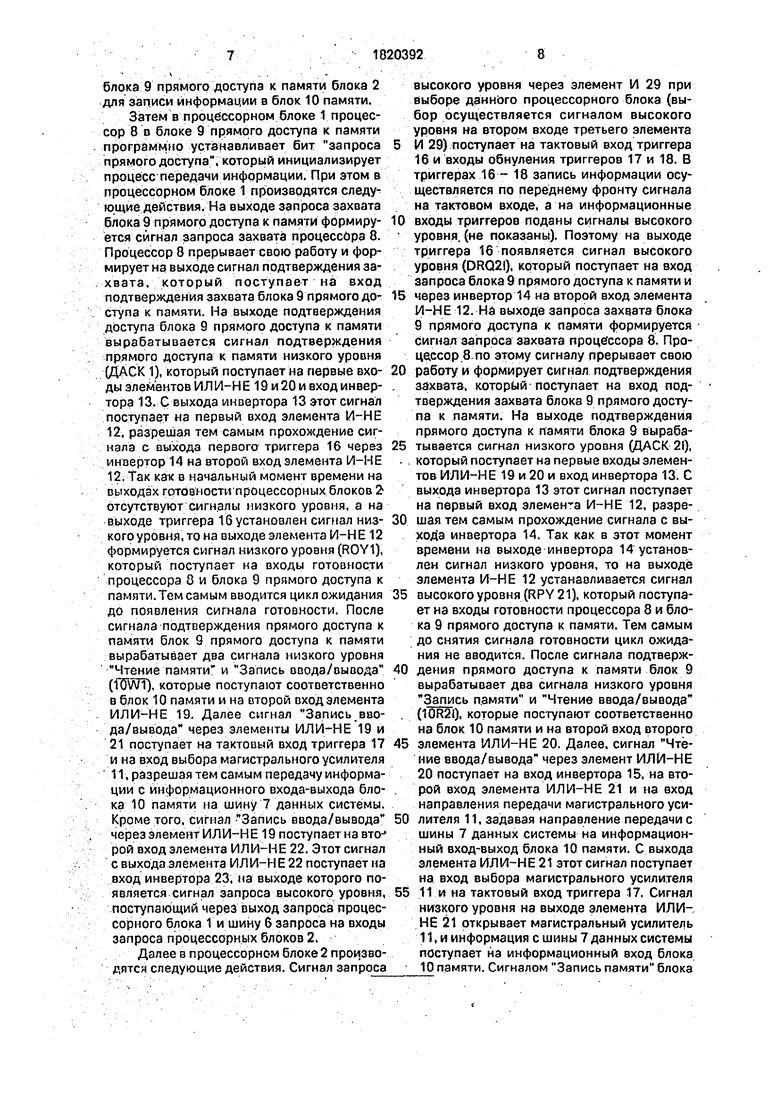

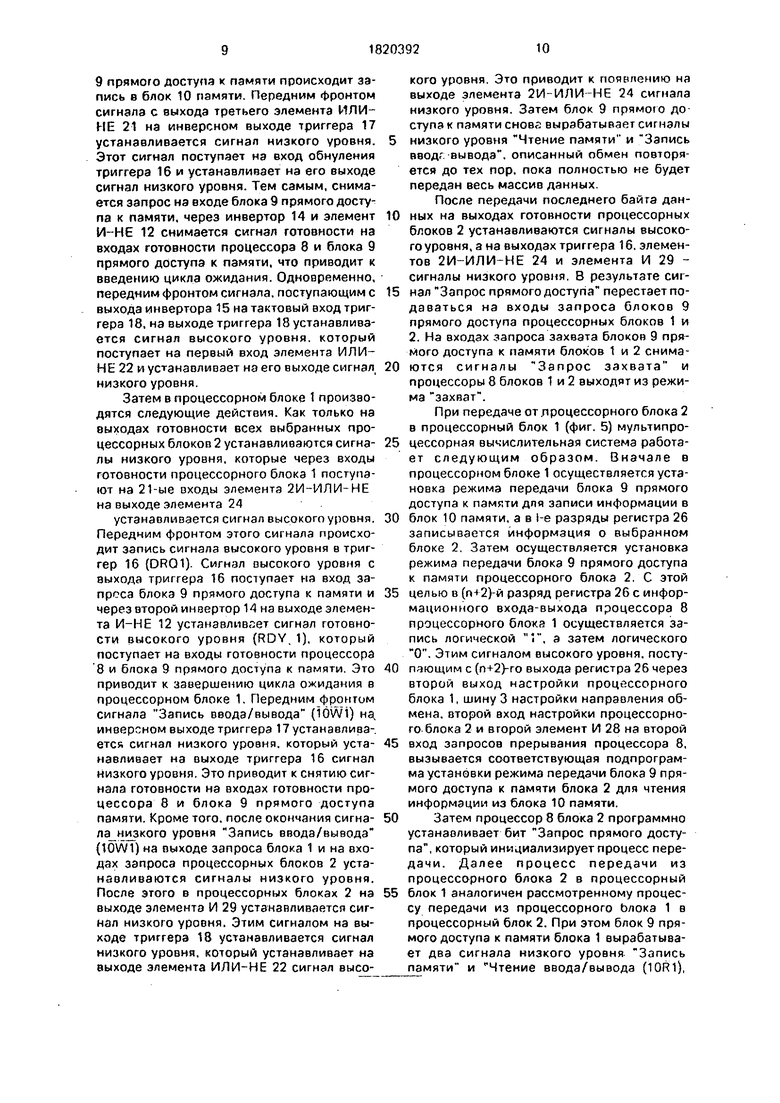

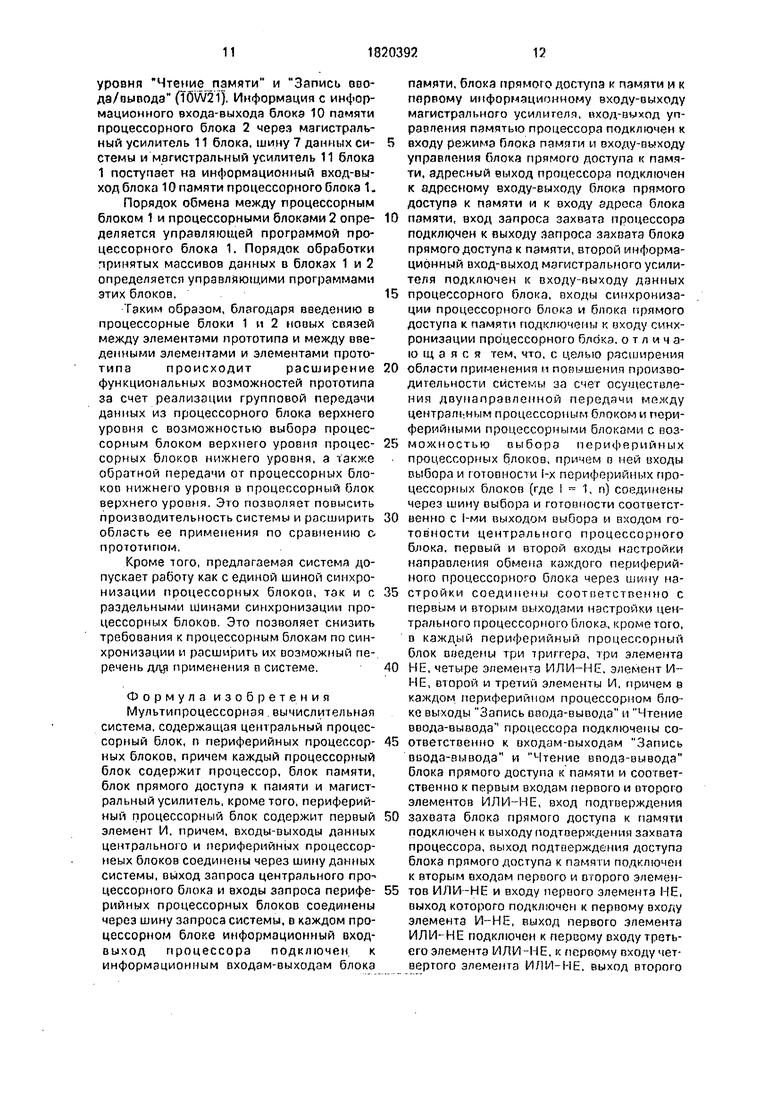

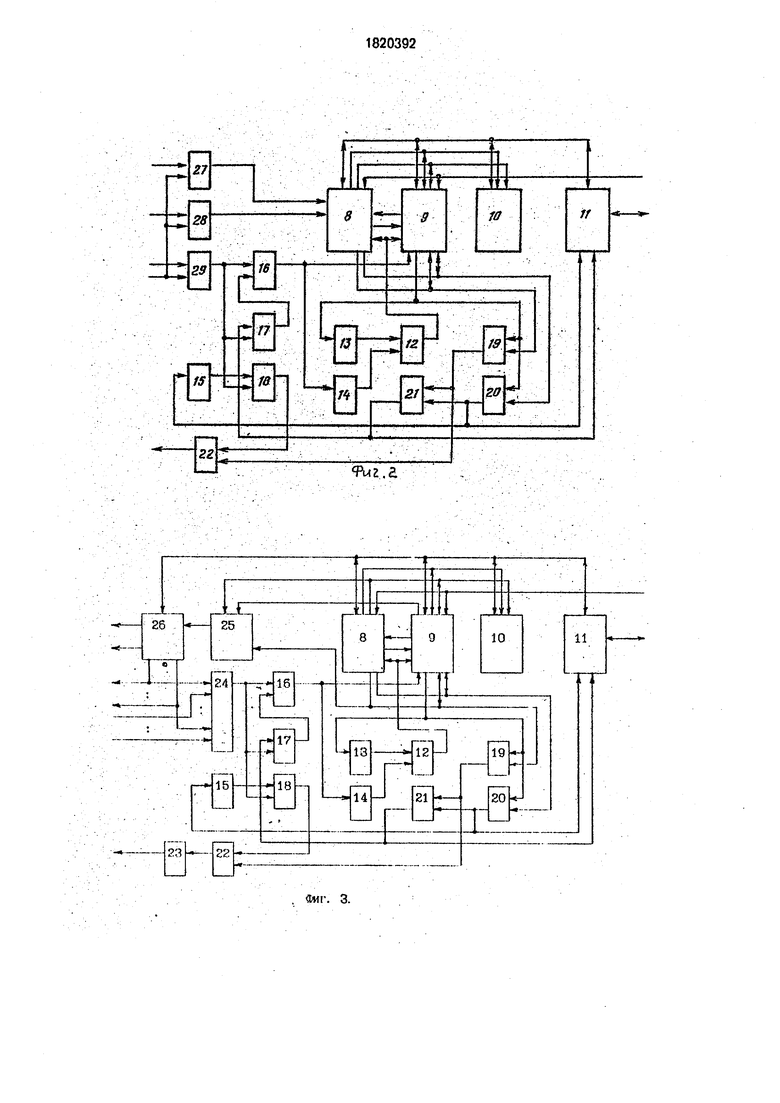

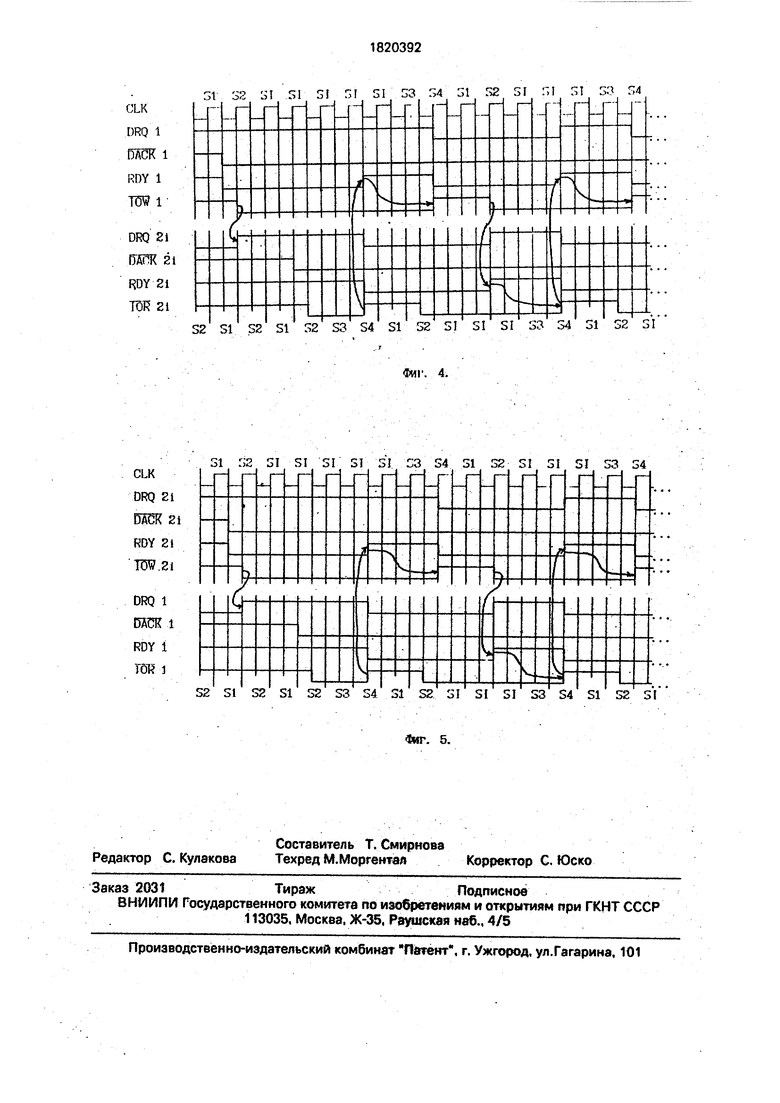

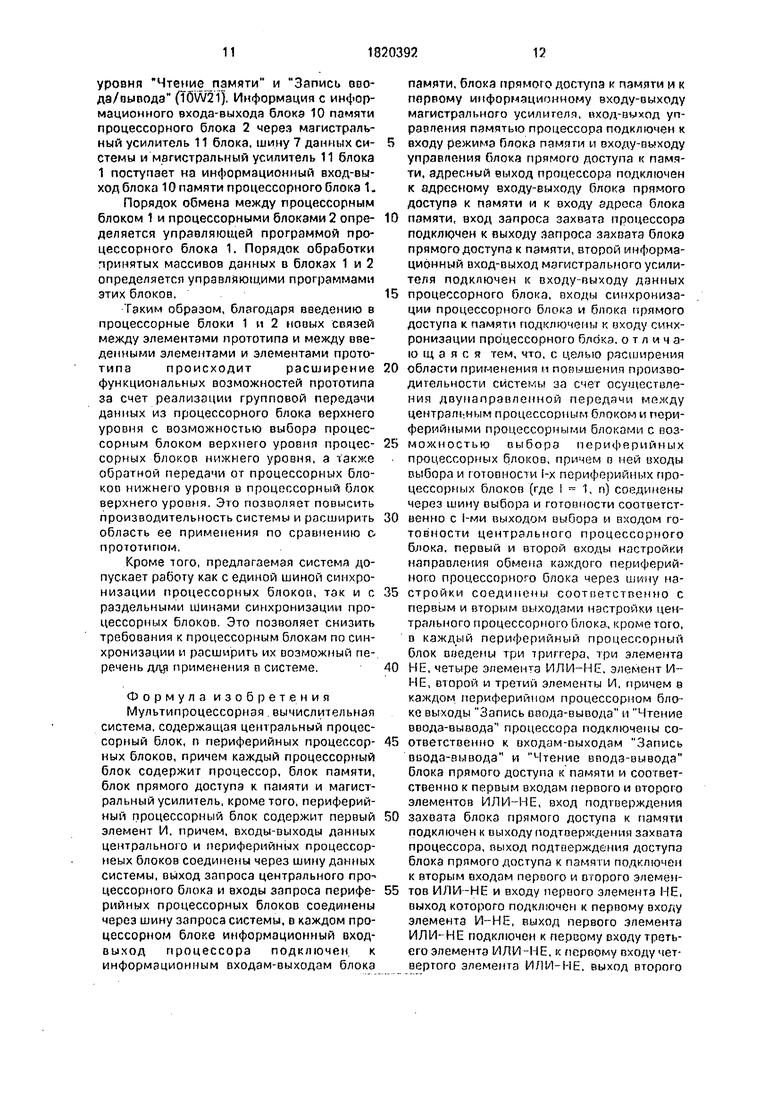

На фиг. 1-3 представлены структурные схемы соответственно системы, периферийного процессорного блока и центрального процессорного блока; на фиг. 4 и 5- временные диаграммы для передачи из центрального процессорного блока в периферийной процессорный блок и для передачи из процессорного блока нижнего уровня в процее-1 сорный блок нижнего уровня..

Система содержит центральный процессорный блок 1, п периферийных процессорных блоков 2, шину 3 направления обмена, шину 4 выбора, шину 5 готовности, шину 6 запросов и шину 7 данных. Каждый .процессорный блок (центральный и периферийный) содержит процессор 8, блок 9 прямого доступа к памяти, блок 10 памяти, магистральный усилитель 1 Т, элемент 12 И- НЕ, первый 13, второй 14 и третий 15 инверторы, :первый 16, второй 17 и третий 18 триггеры, первый 19, второй 20, третий 21 и четвертый 22 элементы ИЛИ-НЕ. Кроме того, процессорный блок 1 верхнего уровня содержит четвертый инвертор 25, элемент 2ИЛИ-ИЛИ-НЕ 24, дешифраторов, регистр 26. Каждый процессорный блок 2 нижнего уровня содержит первый 27, второй 28 и третий 29 элементы И.

В мультипроцессорной вычислительной системе шины данных процессорных блоков 1 и 2 соединены с шиной 7 данных системы, выход запроса центрального процессорного блока 1 и входы запроса периферийных процессорных блоков 2 соединены с шиной 3 запроса системы, 1-е разряды шин 4 выбора и 5 готовности сое- .динены соответственно с 1-ми выходом выбора и входом готовности процессорного блока 1 и соответственно с входом выбора и выходом готовности 1-го процессорного блока 2, первый и второй разряды шины 6 настройки направления обмена соединены соответственно с первым и вторым выходами настройки процессорного блока 1 и соответственно с первым и вторым входами настройки каждого процессорного блока 2, в каждом процессорном блоке информационный вход-выход процессора 8 подключен к информационным входам-выходам блока 10 памяти, блока 9 прямого доступа к памяти и к первому информационному входу-выходу магистрального усилителя 11, вход-выход управления памятью процессора 8 подключен к входу управления блока 10 , памяти и вход-выходу управления блока 9 прямого доступа к памяти, адресный выход

процессора 8 подключен к адресному входу- выходу блока 9 прямого доступа к памяти и к адресному входу блока 10 памяти, вход запроса захвата процессора 8 Подключен к выходу запроса захвата блока 9 прямого

5 доступа к памяти, второй информационный вход-выход магистрального усилителя 11 подключен к шине данных процессорного блока, входы синхронизации процессора 8 и блока 9 прямого доступа к памяти подклго0 чены к входу синхронизации процессорного блока, выходы Запись ввода/вывода и чтение ввода/вывода процессора 8 подключены соответственно к входам-выходам Запись ввода/вывода и Чтение вво5 да/вывода блока 9 прямого доступа к памя. ти и к вторым входам соответственно

элементов ИЛ И-НЕ 19 и 20, вход подтверждения захвата блока 9 прямого доступа к памяти подключен к выходу подтверждения

0 захвата процессора 8, выход подтверждений доступа блока 9 прямого доступа к памяти подключен к первым входам элементов ИЛИ-НЕ 19 и 20 и к входу инвертора 13, выход которого подключен к перво5 му входу элемента И-НЕ 12, выход первого элемента ИЛИ-НЕ 19 подключен к первому входу элемента ИЛИ-НЕ 21 и к второму s ёходу элемента ИЛИ-НЕ 22, выход элемента ИЛИ-НЕ 20 подключен к второму входу

0 элемента ИЛИ-НЕ 21, к входу инвертора 15 и к входу направления передачи магистрального усилителя 11, выход инвертора 15 . подключен к тактовому входу триггера 18, выход элемента ИЛИ-НЕ 21 подключен к

5 тактовому входу триггера 17 и к входу выбо- ра магистрального усилителя 11, выход триггера 18 подключен к первому входу элемента ИЛИ-НЕ 22, инверсный выход триггера 17 подключен к входу обнуления

0 триггера 16, выход которого подключен к входу запроса блока 9 прямого доступа к памяти и к входу инвертора 14, выход инвертора 14 подключен к входу элемента И-НЕ 12, выход которого подключен к входам го5 товности блока 9 прямого доступа к памяти и процессора 8. Кроме того, в процессорном блоке 1 верхнего уровня выход Запись ввода/вывода процессора 8 подключен к первому информационному входу дешифратора 25, выход элемента ИЛИ-НЕ

22 подключен к входу инвертора 23, выход которого подключен к выходу запроса процессорного блока 1,1-й вход элемента 2И- ЙЛИ-НЕ 24, подключен к 1-у выходу регистра 26 и к 1-у выходу выбора процес- сорного блока 1, (п+1)-й вход элемента 2И- ИЛИ-НЁ 24 подключен к 1-у входу .готовности процессорного блока 1, адресный выход процессора 8 подключен к второму информационному входу дешифратора 25, управляющий вход которого подключен к выходу Разрешение адреса блока 9 прямого доступа к памяти, (п+1)-й и (п+2)-ой выходы регистра 26 подключены соответственна к первому и второму выходам на- стройки процессорного блока 1, выход дешифратора 25 подключен к входу записи регистра 26, информационный вход которого подключен к информационному входу- выходу процессора 8. выход элемента 2И-ИЛИ-;НЕ 24 подключен к тактовому входу триггера 16 и к входам обнуления триггеров 17 и 18. В процессорном блоке 2 вход выбора процессорного блока подключен к вторым входам элементов И 27-29, первый и второй входы настройки направления об- мена процессорного блока 2 подключены к первым входам соответственно элементов 14 27 и 28, вход запроса процессорного блока 2 подключен к первому входу элемента И 29, выход которого подключен к тактовому входу триггера 16 и к входам обнуления триггеров 17 и 18, выход элемента ИЛИ-НЕ 22 является выходом готовности процессорного блока 2, выходы элементов И 27.и 28 подключены соответственно к первому и второму входам запросов прерывания процессора 8.

Все блоки и элементы заявляемого уст- ройства хорошо известны и используются по своему прямому назначению. Например, в качестве процессора можно использовать микросхему КР580ИК80, блока прямого до- ступа к памяти-микросхему КР580ИК57, блока памяти-микросхему КР541РУ2А, ма- гистрального усилитсяя-микросхему К589АП16, триггера-микросхему К555ТМ2, элемента И-НЕ - микросхему К555ЛАЗ, элемента И-микросхему К555ЛИ1, элемента ИЛИ-НЕ-микросхему К555ЛЕ1, инвертора- микросхему К555ЛН1. дешифратора-микросхемы К555ИД6, К555ЛА2. К555ЛЕ5.

Мультипроцессорная вычислительная система работает следующим образом (для простоты полагаем, что на входы синхрони- зации процессорных блоков поступает общая частота синхронизации CLK).

В исходном состоянии процессорные блоки 1 и 2 (фиг. 1)при помощи магистральных усилителей 11 (фиг. 2 и 3} отключены от

шины 7 данных системы. При этом на выходах триггеров 16 и 18 устанавливаются сигналы низкого уровня, а на инверсном выходе триггера 17-сигналы высокого уровня. Начальная установка триггеров, например, может осуществляться сигналом (сброс внешнего устройства), поступающим от процессора 8.

В процессорном блоке 1 дешифратор 25 предназначен для выбора адреса регистра 26 с адресного выхода процессора 8. Элемент 2И-ИЛVi-HE 24 предназначен для маскирования неучаствующих в передаче процессорных блоков 2. На 1-е входы этого элемента с I выходов регистра 26 поступает информация с выбранных процессорных блоках 2, а на (п+1)-е входы -сигналы готовности процессорных блоков 2.

Перед началом передачи в процессорных блоках 1 и 2 осуществляется установка режима передачи блока 9 прямого доступа к памяти. Установка режима передачи блоков 9 прямого доступа к памяти процессорных блоков 1 и 2 включает в себя установку режима работы блоковая передача или Блоковая передача по требованию, чтение или запись информации, начального адреса для чтения (записи) информации, количество байт передаваемой (принимаемой) информации, которое в процессорных блоках 1 и 2 должно быть одинаковым. Далее рассматривается работа блоков 9 прямого доступа к памяти в режиме Блоковой передачи.

При передаче от процессорного блока в процессорные блоки 2 (фиг. 4) мультиплек- сорная вычислительная система работает следующим образом.

Вначале в процессорном блоке 1 осуществляется установка режима передачи блока 9 прямого доступа к памяти для чтения информации из блока 10 памяти, а в 1-е разряды регистра 26 записывается информация о выбранных блоках 2, число которых может изменяться до 1 до п. Затем осуществляется установка режима передачи блока 9 прямого доступа к памяти процессорного блока 2. С этой целью в (п+1)-й разряд регистра 26 с информационного входа-выхода процессора 8 процессорного блока 1 осуществляется запись логической 1, а затем логического О. Этим сигналом высокого уровня, поступающим с (п+1)-го выхода регистра 26 через первый выход настройки процессорного блока 1, шину 6 настройки направления обмена, первый вход настройки процессорного блока 2 и первый элемент И 27 на первый вход запросов прерывания процессора 8. вызывается соответствующая подпрограмма установки режима передачи

блока 9 прямого доступа к памяти блока 2 для записи информации в блок 10 памяти.

Затем в процессорном блоке 1 процессор 8 в блоке 9 прямого доступа к памяти программно устанавливает бит запроса прямого доступа, который инициализирует процесс передачи информации. При этом в процессорном блоке 1 производятся следу ющие действия. На выходе запроса захвата блока 9 прямого доступа к памяти формируется сигнал запроса захвата процессора 8. Процессор 8 прерывает свою работу и формирует на выходе сигнал подтверждения захвата, который поступает на вход подтверждения захвата блока 9 прямого доступа к памяти. На выходе подтверждения доступа блока 9 прямого доступа к памяти вырабатывается сигнал подтверждения прямого доступа к памяти низкого уровня (ДАСК1), который поступает на первые входы элементов ИЛИ-НЕ 19 и 20 и вход инвертора 13. С выхода инвертора 13 этот сигнал поступает на первый вход элемента И-НЕ 12. разрешая тем самым прохох дение сигнала с выхода первого триггера 16 через инвертор 14 на второй вход элемента И-НЕ 12. Так как в начальный момент времени на выходах готовности процессорных блоков 21 отсутствуют сигналы низкого уровня, а на выходе триггера 16 установлен сигнал низкого уровня, то на выходе элемента И-НЕ 12 формируется сигнал низкого уровня (ROY1), который поступает на входы готовности процессора 8 и блока 9 прямого доступа к памяти. Тем самым вводится цикл ожидания до появления сигнала готовности. После сигнала подтверждения прямого доступа к памяти блок 9 прямого доступа к памяти вырабатывает два сигнала низкого уровня Чтение памяти и Запись ввода/вывода (fGWT), которые поступают соответственно в блок 10 памяти и на второй вход элемента ИЛИ-НЕ 19. Далее сигнал Запись ввода/вывода через элементы ИЛЙ-НЕ 19 и 21 поступает на тактовый вход триггера 17 и на вход выбора магистрального усилителя 11, разрешая тем самым передачу информации с информационного входа-выхода блока 10 памяти на шину 7 данных системы. Кроме того, сигнал Запись ввода/вывода через элемент ИЛИ-НЕ 19 поступает на BTOJ рой вход элемента ИЛИ-НЕ 22. Этот сигнал с выхода элемента ИЛИ-НЕ 22 поступает на вход инвертора 23, на выходе которого появляется сигнал запроса высокого уровня, поступающий через выход запроса процессорного блока 1 и шину б запроса на входы запроса процессорных блоков 2.

Далее в процессорном блоке 2 производятся следующие действия. Сигнал запроса

высокого уровня через элемент И 29 при выборе данного процессорного блока (выбор осуществляется сигналом высокого уровня на втором входе третьего элемента

И 29) поступает на тактовый вход триггера 16 и входы обнуления триггеров 17 и 18. В триггерах 16 - 18 запись информации осуществляется по переднему фронту сигнала на тактовом входе, а на информационные

входы триггеров поданы сигналы высокого

уровня, (не показаны). Поэтому на выходе триггера 16 появляется сигнал высокого уровня (DRQ2I), который поступает на вход запроса блока 9 прямого доступа к памяти и

через инвертор 14 на второй вход элемента И-НЕ 12. На выходе запроса захвата блока 9 прямого доступа к памяти формируется сигнал запроса захвата процессора 8. Процессор 8. по этому сигналу прерывает свою

работу и формирует сигнал подтверждения захвата, который поступает на вход подтверждения захвата блока 9 прямого доступа к памяти. На выходе подтверждения прямого доступа к памяти блока 9 вырабатывается сигнал низкого уровня (ДАСК 21},

. который поступает на первые входы элементов ИЛИ-НЕ 19 и 20 и вход инвертора 13. С выхода инвертора 13 этот сигнал поступает на первый вход элемента И-НЕ 12, разрешая тем самым прохождение сигнала с выхода инвертора 14. Так как в этот момент времени на выходе инвертора 14 установлен сигнал низкого уровня, то на выходе элемента И-НЕ 12 устанавливается сигнал

высокого уровня (RPY 21), который поступает на входы готовности процессора 8 и блока 9 прямого доступа к памяти. Тем самым до снятия сигнала готовности цикл ожидания не вводится. После сигнала подтверждения прямого доступа к памяти блок 9

вырабатывает два сигнала низкого уровня

Запись п.амяти и Чтение ввода/вывода

(10R21). которые поступают соответственно

на блок 10 памяти и на второй вход второго

элемента ИЛИ-НЕ 20. Далее, сигнал Чтение ввода/вывода через элемент ИЛИ-НЁ 20 поступает на вход инвертора 15, на втррой вход элемента ИЛИ-НЕ 21 и на вход направления передачи магистрального усилителя 11, задавая направление передачи с шины 7 данных системы на информационный вход-выход блока 10 памяти. С выхода элемента ИЛИ-НЕ 21 этот сигнал поступает на вход выбора магистрального усилителя

11 и на тактовый вход триггера 17. Сигнал низкого уровня на выходе элемента ИЛИ- НЕ 21 открывает магистральный усилитель 11, и информация с шины 7 данных системы поступает на информационный вход блока 10 памяти. Сигналом Запись памяти блока

9 прямого доступа к памяти происходит запись в блок 10 памяти. Передним Фронтом сигнала с выхода третьего элемента ИЛИ- НЕ 21 на инверсном выходе триггера 17 устанавливается сигнал низкого уровня. Этот сигнал поступает на вход обнуления триггера 16 и устанавливает на его выходе сигнал низкого уровня. Тем самым, снимается запрос на входе блока 9 прямого доступа к памяти, через инвертор 14 и элемент И-НЕ 12 снимается сигнал готовности на входах готовности процессора 8 и блока 9 прямого доступа к памяти, что приводит к введению цикла ожидания. Одновременно, передним фронтом сигнала, поступающим с выхода инвертора 15 на тактовый еход триггера 18, на выходе триггера 18 устанавливается сигнал высокого уровня, который поступает на первый вход элемента ИЛИ- НЕ 22 и устанавливает на его выходе сигнал низкого уровня.

Затем в процессорном блоке 1 производятся следующие действия. Как только на выходах готовности всех выбранных процессорных блоков 2 устанавливаются сигналы низкого уровня, которые через входы готовности процессорного блока 1 поступают на 21-ые входы элемента 2И-ИЛИ-НЕ на выходе элемента 24

устанавливается сигнал высокого уровня. Передним фронтом этого сигнала происходит запись сигнала высокого уровня в триггер 16 (DR01). Сигнал высокого уровня с выхода триггера 16 поступает на вход запроса блока 9 прямого доступа к памяти и через второй инвертор 14 на выходе элемента И-НЕ 12 устанавливает сигнал готовности высокого уровня (RDY. 1), который поступает на входы готовности процессора 8 и блока 9 прямого доступа к памяти. Это приводит к завершению цикла ожидания в процессорном блоке 1. Передним фронтом сигнала Запись ввода/вывода (10W1) на, инверсном выходе триггера 17 устанавливается сигнал низкого уровня, который устанавливает на выходе триггера 16 сигнал низкого уровня. Это приводит к снятию сигнала готовности на входах готовности процессора 8 и блока 9 прямого доступа памяти. Кроме того, после окончания сигна- ла низкого уровня Запись ввода/вывода (10W1) на выходе запроса блока 1 и на входах запроса процессорных блоков 2 устанавливаются сигналы низкого уровня. После этого в процессорных блоках 2 на выходе элемента И 29 устанавливается сигнал низкого уровня. Этим сигналом на выходе триггера 18 устанавливается сигнал низкого уровня, который устанавливает на выходе элемента ИЛИ-НЕ 22 сигнал высокого уровня. Это приводит к появлению на выходе элемента 2И-ИЛИ-НЕ 24 сигнала низкого уровня. Затем блок 9 прямого до ступа к памяти снова вырабатывает сигналы 5 низкого уровня Чтение памяти и Запись вводг; вывода, описанный обмен повторяется до тех пор, пока полностью не будет передан весь массив данных.

После передачи последнего байта дан0 ных на выходах готовности процессорных блоков 2 устанавливаются сигналы высокого уровня, а на выходах триггера 16. элементов 2И-ИЛИ-НЕ 24 и элемента И 29 - сигналы низкого уровня. В результате сиг5 нал Запрос прямого доступа перестает подаваться на входы запроса блоков 9 прямого доступа процессорных блоков 1 и 2. На входах запроса захвата блоков 9 прямого доступа к памяти блоков 1 и 2 снима0 ются сигналы Запрос захвата и процессоры 8 блоков 1 и 2 выходят из режима захват.

При передаче отяроцессорного блока 2 в процессорный блок 1 (фиг. 5) мультипро5 цессорная вычислительная система работает следующим образом. Вначале в процессорном блоке 1 осуществляется установка режима передачи блока 9 прямого доступа к памяти для записи информации в

0 блок 10 памяти, а в 1-е разряды регистра 26 записывается информация о выбранном блоке 2, Затем осуществляется установка режима передачи блока 9 прямого доступа к памяти процессорного блока 2. С этой

5 целью в (ги2)-й разряд регистра 26 с информационного входа-выхода процессора 8 процессорного блока 1 осуществляется запись логической Г, а затем логического О. Этим сигналом высокого уровня, посту0 лающим с (п+2)-го выхода регистра 26 через второй выход настройки процессорного блока 1, шину 3 настройки направления обмена, второй вход настройки процессорного блока 2 и второй элемент И 28 на второй

5 вход запросов прерывания процессора 8, вызывается соответствующая подпрограмма установки режима передачи блока 9 прямого доступа к памяти блока 2 для чтения информации из блока 10 памяти.

0 Затем процессор 8 блока 2 программно устанавливает бит Запрос прямого доступа, который инициализирует процесс передачи. Далее процесс передачи из процессорного блока 2 в процессорный

5 блок 1 аналогичен рассмотренному процессу передачи из процессорного блока 1 в процессорный блок 2. При этом блок 9 прямого доступа к памяти блока 1 вырабатывает два сигнала низкого уровня Запись памяти и Чтение ввода/вывода (10R1),

уровня Чтение памяти и Запись ввода/вывода (TOW2T). Информация с информационного входа-выхода блока 10 памяти процессорного блока 2 через магистральный усилитель 11 блока, шину 7 данных системы и магистральный усилитель 11 блока 1 поступает на информационный вход-выход блока 10 памяти процессорного блока 1.

Порядок обмена между процессорным блоком 1 и процессорными блоками 2 определяется управляющей программой процессорного блока 1. Порядок обработки принятых массивов данных в блоках 1 и 2 определяется управляющими программами этих блоков.

Таким образом, благодаря введению в процессорные блоки 1 и 2 новых связей между элементами прототипа и между введенными элементами и элементами прототипа происходит расширение функциональных возможностей прототипа за счет реализации групповой передачи данных из процессорного блока верхнего уровня с возможностью выбора процессорным блоком верхнего уровня процессорных блоков нижнего уровня, а также обратной передачи от процессорных блоков нижнего уровня в процессорный блок верхнего уровня. Это позволяет повысить производительность системы и расширить область ее применения по сравнению с- прототипом.

Кроме того, предлагаемая система допускает работу как с единой шиной синхронизации процессорных блоков, так и с раздельными шинами синхронизации процессорных блоков. Это позволяет снизить требования к процессорным блокам по синхронизации и расширить их возможный перечень дл применения п системе.

Формула изобретения Мультипроцессорная.вычислительная система, содержащая центральный процессорный блок, п периферийных процессорных блоков, причем каждый процессорный блок содержит процессор, блок памяти, блок прямого доступа к памяти и магистральный усилитель, кроме того, периферийный процессорный блок содержит первый элемент И, причем, входы-выходы данных центрального и периферийных процессор- неых блоков соединены через шину данных системы, выход запроса центрального процессорного блока и входы запроса периферийных процессорных блоков соединены через шину запроса системы, в каждом процессорном блоке информационный вход- выход процессора подключен к информационным входам-выходам блока

памяти, блока прямого доступа к. памяти и к первому информационному входу-выходу магистрального усилителя, вход-выход управления памятью процессора подключен к

входу режима блока памяти и входу-выходу управления блока прямого доступа к памяти, адресный выход процессора подключен к адресному входу-выходу блока прямого доступа к памяти м к входу адреса блока

0 памяти, вход запроса захвата процессора подключен к выходу запроса захвата блока прямого доступа к памяти, второй информационный вход-выход магистрального усилителя подключен к входу-выходу данных

5 процессорного блока, входы синхронизации процессорного блока и блока прямого доступа к памяти подключены к входу синхронизации процессорного блока, отличающаяся тем, что, с целью расширения

0 области применения м повышения производительности системы за счет осуществления двунаправленной передачи между центральным процессорным блоком и периферийными процессорными блоками с воз5 можностью выбора периферийных процессорных блоков, причем о ней входы выбора и готовности 1-х периферийных процессорных блоков (где I 1, п) соединены через шину выбора и готовности соответст0 венно с i-ми выходом выбора и входом готовности центрального процессорного блока, первый и второй входы настройки направления обмена каждого периферийного процессорного блока через ши-ну на5 стройки соединены соответственно с первым и вторым выходами настройки центрального процессорного блока, кроме того, п каждый периферийный процессорный блок введены три триггера, три элемента

0 НЕ, четыре элемента ИЛИ-НЕ, элемент 1/1- НЕ, второй и третий элементы И, причем в каждом периферийном процессорном блоке выходы Запись ввода-вывода и Чтение ввода-вывода процессора подключены со5 ответственно к входам-выходам Запись ввода-вывода и Чтение вподз-вывода блока прямого доступа к памяти и соответственно к первым входам первого и второго элементов ИЛИ-НЕ, вход подтверждений

0 захвата блока прямого доступа к памяти подключен к выходу подтверждения захвата процессора, выход подтверждения доступа блока прямого доступа к памяти подключен к вторым входам первого и второго элемен5 тов ИЛИ-НЕ и входу первого элемента НЕ, выход которого подключен к первому входу элемента И-НЕ, выход первого элемента ИЛИ-НЕ подключен к первому входу третьего элемента ИЛИ-НЕ, к первому входу четвертого элемента ИЛИ-НЕ. выход второго

элемента ИЛИ-НЕ подключен к второму входу третьего элемента ИЛИ-НЕ, входу второго элемента НЕ и входу направления передачи магистрального усилителя, выход третьего элемента ИЛИ-НЕ подключен к тактовому входу первого триггера и входу выбора магистрального усилителя, выход второго элемента НЕ подключен к тактовому входу второго триггера, выход второго триггера подключен к второму входу четвертого элемента ИЛИ-НЕ, инверсный выход третьего триггера подключен к входу обнуления третьего триггера, выход которого подключен к входу запроса блока прямого доступа к памяти и входу третьего элемента НЕ, выход третьего элемента НЕ подключен к второму входу элемента И-НЕ, выход которого подключен к входам готовности блока прямого доступа к памяти и процессора, вход выбора процессорного блока подключен к первым входам первого, второго и. третьего элементов И, первый и второй входы выбора режима процессорного блока подключены соответственно к вторым входам первого и второго элементов И, вход запроса процессорного блока подключен к второму входу третьего элемента И, выход которого подключен к тактовому входу второго триггера и входам обнуления второго и третьего триггеров, выход четвертого элемента ИЛИ-НЕ является выходом готовности периферийного процессорного блока, выходы первого и второго элементов И подключены соответственно к первому и второму входам запросов прерывания процессора, кроме того, в центральный процессорный блок введены элемент И-НЕ. три триггера, четыре элемента НЕ, четыре элемента ИЛИ-НЕ, дешифратор, регистр иэле- мент 2И-ИЛИ-НЕ, причем в центральном процессорном блоке выходы Запись ввода- вывода и Чтение ввода-вывода процессора подключены соответственно к входам-выходам Запись ввода-вывода и. Чтение ввода-вывода блока прямого доступа к памяти и к первым входам соответ- ственно первого и второго элементов ИЛИ-НЕ, вход подтверждения захвата блока прямого доступа к памяти подключен к выходу подтверждения захвата процессора, выход подтвержения доступа блока прямого доступа к памяти подключен к вторым

входам первого и второго элементов ИЛИ- НЕ и входу первого элемента НЕ, выход которого подключен к первому входу элемента И-НЕ, выход первого элемента ИЛИ- 5 НЕ подключен к первому входу третьего элемента ИЛИ-НЕ и первому входу четвертого элемента ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ подключен к второму входу третьего элемента ИЛИ-НЕ, входу второго 0 элемента НЕ и входу направления передачи магистрального усилителя, выход третьего элемента ИЛИ-НЕ подключен к тактовому входу первого триггера и входу выбора магистрального усилителя, выход второго эле5 мента НЕ подключен к тактовому входу второго триггера, выход второго триггера подключен к второму входу четвертого элемента ИЛИ-НЕ, инверсный выход первого триггера подключен к входу обнуления

0 третьего триггера, выход которого подключен к входу запроса блока прямого доступа к памяти и входу третьего элемента НЕ, .выход третьего элемента НЕ подключен к второму входу элемента И-НЕ, выход которого

5 подключен к входам готовности блока прямого доступа к памяти и процессора, выход Запись ввода-вывода процессора подключен к первому информационному входу дешифратора, выход четвертого элемента

0 ИЛИ-НЕ, подключен к входу четвертого элемента НЕ, выход которого подключен к выходу запроса процессорного блока, 1-й вход элемента 2И-ИЛИ-НЕ (где I 1...п) подключен к i-му выходу регистра и 1-му вы5 ходу выбора процессорного блока, (п+1)-й вход элемента 2И-ИЛИ-НЕ подключен к входу готовности процессорного блока, адресный выход процессора подключен к второму информационному входу

0 дешифратора, управляющий вход которого подключен к выходу Разрешение адреса блока прямого доступа к памяти, (п+1)-й и (п+2)-й выходы регистра подключены соответственно к первому и второму выходам

5 режима процессорного блока, выход дешифратора подключен к входу записи регистра, информационный вход которого поразрядно подключен к информационному входу-выходу процессора, выход элемента

0 2И-ИЛИ-НЕ, подключен к тактовому входу первого триггера и к входам обнуления второго и третьего триггеров.

CLK DRQ 1 ПЛПК 1 RDY 1 ТШ I

DRQ21 ВШ 21 RDY 21 TOR 21

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистрали микроЭВМ с магистралью периферийных устройств | 1988 |

|

SU1508220A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Система обработки данных | 1980 |

|

SU1003063A1 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Система сбора и обработки информации | 1987 |

|

SU1424024A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1982 |

|

SU1269142A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании информационно-управляющих системе высокой скоростью передачи данных. Целью изобретения является расширение области применения и повышение производительности системы за счет реализации двунаправленной передачи между центральным процессорным блоком и периферийными процессорными блоками с возможностью выбора периферийных процессорных блоков. Система содержит центральный процессорный блок 1, п периферийных процессорных блоков, шину 3 направления обмена, шину 4 выбора, шину 5 готовности, шину 6 запросов, шину 7 данных. 3 ил.

51 32 SI SI SI SI SI G3 54 SI 32 SI SI SI S3 S4

52 SI S2 SI 52 S3 S4 31 S2 SI SI SI S3 S4 SI 52 SI

ФИГ. 4.

Фиг. 5.

| Радиоприемное устройство | 1940 |

|

SU57756A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Авторское свидетельство СССР № 1345891, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1993-06-07—Публикация

1991-03-29—Подача